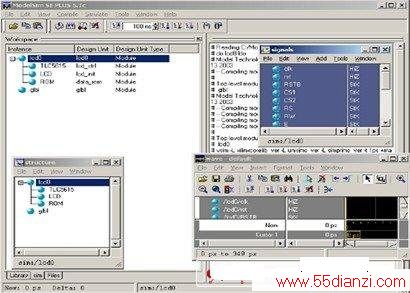

图13 中Module View 窗口中选中代码的最顶层模块。而后如图 13 蓝色部位所示,在 Process View 窗口中的 Launch Modelsim Simlator,将自动打开 Modsim,并且已将当前 project 的相关信息加载到了 Modsim 中。如图 14 所示。要注意的是,后仿真也是如此调用 Modsim。关于 Modsim 的使用请参考相关文档。如果需要仿真的不是最顶层模块,则在 Module View 窗口中选中相应的代码文件,用同样的步骤调用仿真。

图14 调用的 Modsim

4.约束文件

ISE 是一款基于约束的开发工具。在进行高速数字电路设计的时候,需要在综合、映射、布线时附加约束条件,以便控制综合、映射、布线过程,使设计满运行速度,使用资源和引脚位置等要求。约束包括时序约束、分组约束和区域约束。在本文中,将介绍最常用的Constraints Editor 约束编辑器,以及时序约束和引脚绑定(该两者最为基本)。首先,像第二步编写代码文件中一样建立约束文件(.ucf 文件),在本文中,如图 15 所示,可以看到 LCD_c.ucf 文件即为一个约束文件。新建时,唯一的不同是在图 8 中左面对话框中应选择 Implementation Constraints File。同样地,如果已经有现成的约束文件,也可以通过和代码文件相同的方法导入。如图 15 所示,在 Module View 窗口中选中代码的最顶层模块,而后在 ProcessView 窗口中双击 Create Timing Constraints或者 Create Area Constraints,将自动打开 Constraints Editor 约束编辑器。

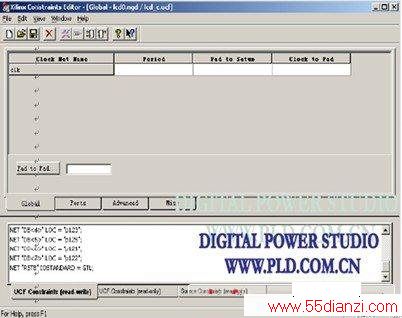

需要注意的是,双击 Assign PACkage PINs 将打开引脚与区域约束编辑器PACE,由于 Constraints Editor 约束编辑器完全可以完成引脚绑定的功能,对于PACE 的使用,本文不再进行详细讨论。Constraints Editor 如图 16 所示。

图15 在project navigator 中调用 Constraints Editor

图16 Constraints Editor 界面

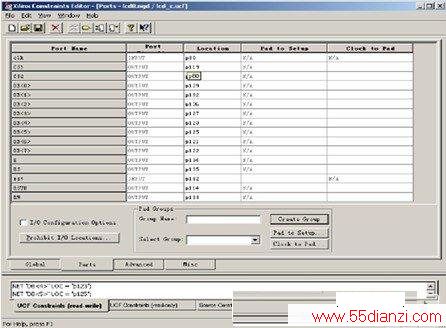

如图 16 所示,共有四类约束界面,Global 为附加全局约束,Ports 为附加端口约束,Advanced 为附加分组约束和时序约束,Misc 为附加专用约束。常用的是 Ports,其中可以进行引脚绑定,如图 17 所示。双击对应信号的LOCation 框,可以进行输入。在引脚号前必须加上字母 p。在这次 LCD 实验中,可以直接导入 digital power 提供的 lcd_c.ucf 文件,也可以自己在 Constraints Editor 中如图 17 中所示一样进行设置。

图17 附加引脚约束

通过以上设置,就完成了约束,在这里附加提到一点就是,在 Constraints Editor 中,下方的对话框将显示 ucf 文件的内容。约束文件也可以通过文本输入的方式完成,在图 15 中双击 Edit Constraints(Text)即可。5.综合与实现

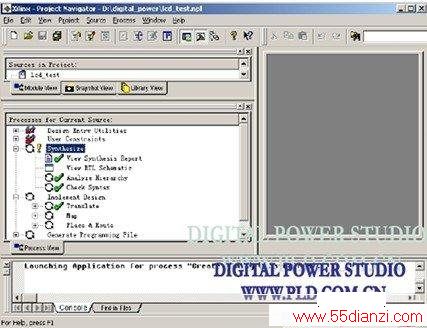

在进行完约束以后,就可以进行综合与约束了。综合与实现的工作将由 ISE自动完成,用户通过约束文件和对 properties 选项控制实现对整个过程的控制。整个过程将产生映射、布线等一系列时序报告以及 RTL schematIC View,还可以利用 XPower 进行功耗分析,便于用户对综合与实现的结果有个详细的了解。

综合与实现如图 18 所示。

图18 实现与综合

在 process view 中,Synthesize 为综合过程,Implement Design 为实现过程。在其上点击右键选择 properties 选项,将进入 properties 对话框,可以对过程要求进行控制。一般直接点击右键选择 run all 即可。

6.下载

最后就只剩下下载工作了。在下载之前,必须先将硬件准备好。首先,如图 19 所示,连接好电源线。

图19 连接电源线

其次,如图 20 所示,连接好下载线。

图20 连接下载线

在硬件准备好后,如图 21 所示,双击 Configure DevICe(iMPACT),打开 ISE中集成的芯片下载具 iMPACT。

图21 打开 iMPACT

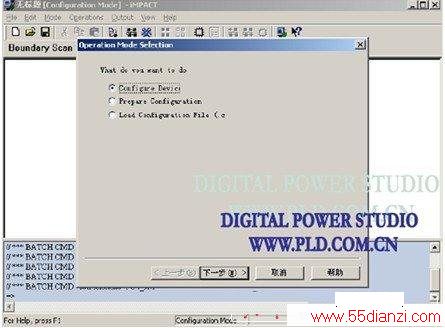

iMPACT 如图 22 所示。

图22 iMPACT

在图 22 中,点击下一步。

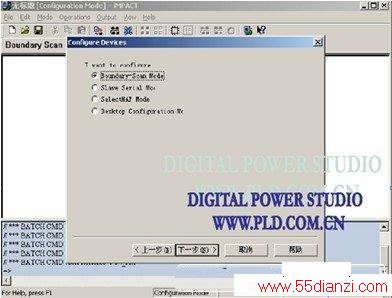

图23 选择配置 FPGA 的方式

如图 23 所示,是选择配置 FPGA 的方式,选择第一项边界扫描(JTAG)方式。点击下一步。进入下一界面后,点击完成。若硬件连接正确,将进入图 24 所示界面,XC2S200 芯片将被自动搜索到,显示出来。若硬件连接有问题,可以在正确改接硬件电路以后,在空白出点击右键选择 Initialize Chain 略过以上一些步骤直接开始搜索芯片。若连接有问题,将弹出对话框选择连接端口,一般采用默认的 LPT 端口(并口)即可。

双击图中 XC2S200 的图标,在弹出的窗口中选择你所需要下载的 bit 文件,点击 ok 即可。在 XC2S200 上点击右键选择 PROGRAMME,并在弹出的对话框中选择programme 将开始下载。

下载成功后如图所示。

这时你就可以在液晶上看到如图 2 所示的流氓兔效果了。

本文关键字:开发 DSP/FPGA技术,单片机-工控设备 - DSP/FPGA技术