TAP控制器、控制管脚(测试数据输入端口TDl、测试数据输出端口TD0、测试时钟TCK、测试方式选择TMS)和数字边界模块(DBM)是IEEEll49.1标准特征。TAP控制器是一个时序电路,由TMS和TCK信号驱动。TAP控制器提供了边界扫描测试所需的全部过程,包括:(1)提供信号将指令移入指令寄存器中。(2)提供信号将测试数据移入测试数据寄存器中,并把测试响应数据从这些寄存器移出。(3)提供信号完成测试操作,如捕获、移位、更新测试数据等。

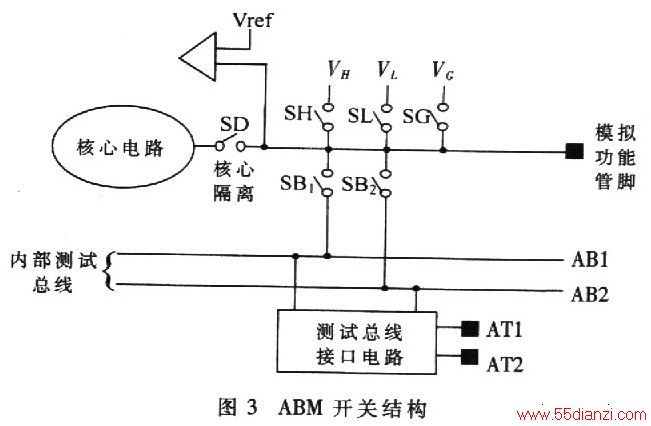

ABM是一种模拟电路边界扫描单元,它具有由数字电路构成的移位寄存器、更新寄存器和控制逻辑。移位寄存器、更新寄存器用来进行数字信号的输入输出。控制逻辑的作用是控制模拟功能管脚上的概念开关,其开关结构如图3所示。

各模拟功能管脚通过ABM的概念开关矩阵和测试总线接口电路,与模拟测试访问口ATl、A2相连。外界模拟测试激励可通过l或2条模拟信号通路施加到某l或2个模拟管脚上,模拟功能引脚上的模拟测试响应也可通过另一条模拟测试通路输出到外界,由模拟测试响应处理器处理。

边界扫描测试受控系统的工作程序是:泓试主控系统产生满足IEEEll49.4协议的测试信号;将数字测试激励数据以串行方式由受控系统的TDI输入边界扫描寄存器;将模拟测试激励给ATl;通过TMS发送测试控制命令,经TAP控制器控制数字和模拟边界扫描单元完成测试数据的加载和测试响应数据的采集。最后,数字测试响应数据以串行扫描方式由TD0送出,模拟测试响应数据由AT2送出,交由测试主控系统进行分析处理。

2.2 测试主控系统体系结构

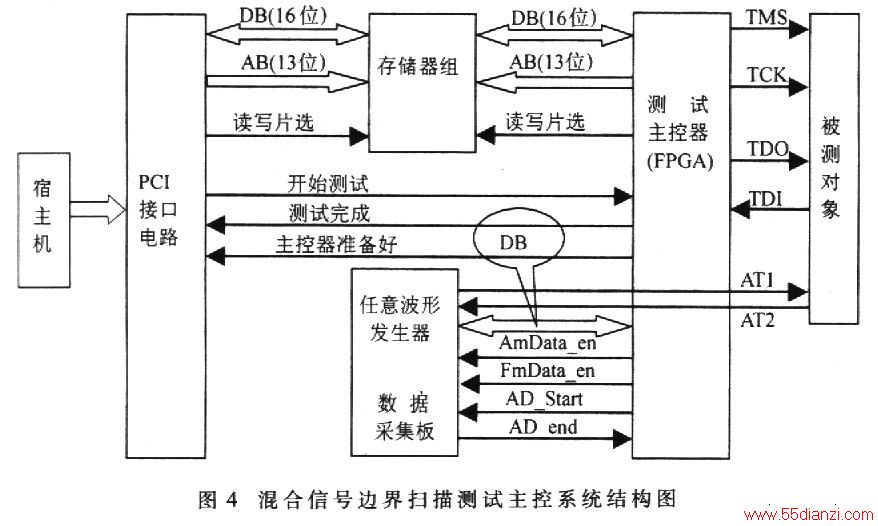

整个测试主控系统主要由宿主机、PCI接口电路、存储器组(包括测试程序存储器和测试响应存储器)、测试主控器、任意波形发生器和数据采集板组成,其结构凰如图4所示。

PCI总线可以实现PC机与外部元件的高速数据传输。PLX公司开发的PCl9054是一种PCI接口控制芯片,符合PCI局部总线规范V2.2,其峰值传输速率为132Mbps(32位PCI数据线)。存储器组用于存放测试代码和测试响应数据,由PCl9054和主控器共享访问,即对存储器组的访问包括PCI9054向存储器组写入测试代码和从存储器组读取测试响应数据,以及主控器从存储器组中读取测试代码和向存储器组写入测试响应数据。

可在主控器的设计中增加1个HOLD输入引脚,当HOLD为高电平时,使主控器的数据线和地址线变为高阻态。这样,根据系统的运行流程,当PCI9054向存储器组写入测试代码或从其读人测试响应数据时,由于这些过程只发生在测试进行前或测试结束后,可以使主控器的HOLD引脚为高电平,主控器的数据线与地址线为高阻态,而不影响PCl9054对存储器组的访问。也就是说,PCI9054和主控器对存储器组的访问采用了分时的原则,同时由于主控器的运行是由PC机通过PCI9054来控制的,所以PCI9054对存储器组的访问相对优先。

主控器是本系统的核心部分,其主要功能包括:访问存储器,将测试代码转换为满足IEEEll49.4标准的边界扫描测试信号,进行数据比较等。所以主控器实际上是一个简单的RISC微处理器。主控器的体系结构由四部分组成:命令解释器、存储器接口,任意波形发生器和数据采集板控制电路、提供边界扫描测试接口信号的几AG接口。其存储器接口由16位数据线DB[15:O]和13位地址线AB[12:0]、写信号WR、读信号RD、复位信号RESET及时钟信号CLOCK组成。

整个主控系统的工作流程是:宿主机软件根据被测对象和测试图形生成主控器可以执行的测试代码并通过PCI总线传送到系统的存储器组中;接收到开始测试信号后,主控器开始执行存储器中的代码,生成TCK、TMS信号给被测对象;直接生成数字测试激励数据给TD1,或由主控器送模拟激励幅度、频率等数据给任意波形发生器,由波形发生器生成相应的模拟测试激励,经ATl脚给被测对象。

主控器接收从TDO脚送入的数字测试响应数据;数据采集板将AT2脚采集到的模拟测试响应(包括幅度和相位信息)转换成数字数据送给测试主控器。主控器将这些响应信号与预期信号进行比较,或将其存于存储器中。若比较结果与预期响应不相符,即停止提供测试信号并向宿主机申请中断。存于存储器组中的数据可以通过PCI总线读回宿主机进行诊断,以查找出故障的位置和原因。

3 分析

(1)利用广义特征分析进行故障隔离,从原理上讲是对电路进行功能测试,因此一般情况下是模拟实际电路工作环境。若作为机内自检的故障隔离,仅是故障检测后的故障隔离,不需注入信号,则库函数的自然映射为单射这一条件可去掉.但作为电路单元(PCB)的测试,一般需加入激励信号。广义特征分析法利用库函数映射的思想,将传统的各种故障字典法进行统一描述,并推广到各种模拟或数字电路的诊断中,因此测试设备应能满足任意波形存储和任意波形产生的要求。实践证明,该方法对模数混合电路的测试是可行的。

(2)在电路设计中将棍合电路分为可单独测试的模拟模块和数字模块,在测试时分别对模拟和数字部分进行测试。需要注意的是,即使模拟测试与数字测试的结果完全合格,也并不表示电路没有故障,因为二者间的连接部分出现一点错误,都会导致电路失效,所以无论整体功能与模块化的测试结果间有怎样确定的关系,在测试项目中,保留一些整体功能测试是必须的。

(3)IEEEll49.4标准的混合信号测试总线方案对模拟信号的测试精确度目前还不能达到理想水平。测试实践表明,1kΩ的电阻其测量误差可控制在1%以下,电抗为1kΩ的电感和电容,其测量误差可控制在5%以下;其他分立元件参数值的测量误差会更大。混合信号电路中.分立元器件的参数值随使用时间的推移而发生变化,这也给故障诊断带来很大的困难。另外,对于高频或射频混合信号电路,IEEEll49.4标准的运用受到限制。

本文关键字:暂无联系方式DSP/FPGA技术,单片机-工控设备 - DSP/FPGA技术