内容摘要:以ALTEr公司的FPGA为硬件平台,以QUARTusⅡ为设计工具,来实现该直扩/跳频混合发射系统。顶层采用图形设计方式,各个模块均采用Verilog语言进行设计。编码模块采用了RS(255,223)码与卷积码(2,1,7)相结合,扩频模块采用GOLD码序列进行扩频,调制模块采用MSK调制。仿真结果表明:各个仿真模块均满足设计的要求,整个系统输出稳定无毛刺,达到了预期的效果。

关键词:直扩/跳频;发射机;Verilog HDL;MSK

引言

扩频通信是将待传输的信息数据用伪随机序列进行调制,实现频谱扩展后再发射出去进行传输。在接收端,使用与发射端相同的伪随机码对接收到的信号进行相关处理,恢复出原来的信息。直扩/跳频(DS/FH)混合模式是一种有效的方法,它结合了直扩扩频与跳频扩频的优点,消除了直扩扩频与跳频扩频的局限性,可广泛应用于军事通信中,达到更好的抗干扰效果。

该设计以FPGA为硬件平台,以QuartusⅡ为设计工具来实现直扩/跳频(DS/FH)发射机的。顶层采用图形设计方式,各个模块均采用Veri log语言进行设计,编码模块采用了RS(255,223)码与卷积码(2,1,7)相结合,扩频模块采用GOLD码序列进行扩频,调制模块采用MSK调制。

1 发射系统的总体框图

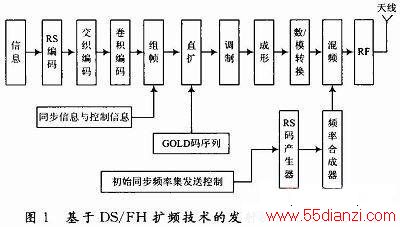

所设计的发射机系统主要包括:信道编码器、组帧电路、直扩部分、成形电路、调制器、数/模转换器、频率合成器、RS码产生器、混频器、功放、天线等。组成框图如图1所示。

射频部分主要采用跳频技术将中频信号进行频谱搬移,通过跳频调制和高频混频两步完成,用到频率合成技术和滤波等,这主要通过硬件实现。基带部分则完成FPGA的设计,下面将详细介绍。

主要可以划分为以下几个模块:编码模块、组帧模块、扩频模块、调制模块。编码模块完成信息的RS编码和卷积编码;组帧模块在经过编码的数据前面添加位同步和帧同步信息;直接序列扩频模块将信号频谱扩展到一个很宽的频段上;MSK调制模块利用扩频序列去调制载波,将扩频调制信号搬移到射频上去,然后经过功率放大,D/A变换发送出去。

2 各个发射模块的功能介绍及设计

2.1 编码模块设计

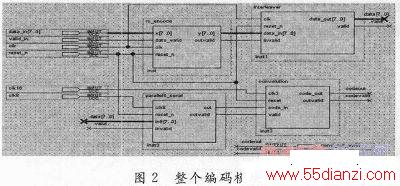

整个编码实现由4级组成,分别是RS编码、交织、并/串转换和卷积编码,如图2所示。

2.2 组帧模块设计

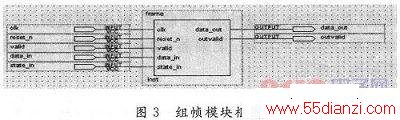

在信息发送端,经过编码的数据插入状态标识组成数据帧。再加上同步序列、帧同步,组成1帧。组帧器的设计思路:首先将输入数据放入一个寄存器,输出12 b的同步序列,以及帧同步码——巴克码;之后,将保存的部分状态标识数据依次输出;最后,通过移位法将输人数据依次移位输出,输完之后加上帧尾。设计结果如图3所示。

图3中:

clk:时钟采样信号,组帧器在其上升沿处数据采样,并进行组帧运算。

reset_n:组帧器异步复位控制信号。定义为1表示不进行复位操作,采样数据有效,组帧器正常操作;定义为0表示进行复位操作,采样数据寄存器清零,组帧器清零。

data_in:信启、数据的输入端口,其位宽为1 b。

state_in:状态标识输入比特。

valid:输入数据的有效位。

data_out:组帧后码字输出端口,其位宽为1 b。

outvalid:输出数据的有效位。

2.3 扩频模块设计

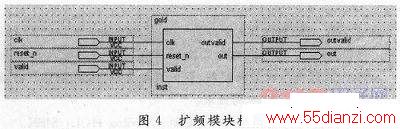

GOLD码序列产生器的设计结果如图4所示。在整个模块中分为2个进程。一是在时钟上升沿到来并且复位结束时,进行m序列优选对的算法,分别将两个31位的m序列值存入寄存器中,初值都为“11111”。另一个进程通过输入位valid进行判断。通过valid=1,进行对位异或运算,计算GOLD码,产生一组码后,将其保存,然后在连续零处添加1个零,然后输出,其余的码组通过移位实现,这样就生成了32 b×32 b的GOLD码,串行输出。

图4中:

clk:时钟采样信号,GOLD码编码器在其上升沿处数据采样,并进行产生GOLD码运算。

reset_n:GOLD码编码器异步复位控制信号。定义为1表示不进行复位操作,数据有效,GOLD码编码器正常操作;定义为0表示进行复位操作,数据寄存器清零,并进行初值赋值。

valid:开启计算GOLD码的开关。

out:GOLD码输出端口,其位宽为1 b。

outvalid:输出数据的有效位。

2.4 调制模块设计

根据MSK的基本原理,并且根据公式![]() 改变频率控制字的值即可改变NCO的输出频率。其中FCW为用二进制初码表示的频率控制字。fin为NCO的采样频率,n为频率控制字的位数,相当为输入二进制初码的位数。即为输出所要求的频率。

改变频率控制字的值即可改变NCO的输出频率。其中FCW为用二进制初码表示的频率控制字。fin为NCO的采样频率,n为频率控制字的位数,相当为输入二进制初码的位数。即为输出所要求的频率。

MSK调制器的实现需要3个必要条件。一是在码元转换时刻,进行FPGA中控制NCO的频率输出的切换。二是相位连续。由于NCO输出信号的相位始终能保持连续,满足了条件。三是在一个符号周期内必须包含1/4载波周期的整数倍。根据必要条件三,可以得出下式:

![]()

因此,当fs=4 MHz,即输入MSK调制器的符号采样率为4 MHz,当n=20时,则fc为20 MHz,即载波频率为20 MHz。因此,便完成了MSK调制器的FPGA实现。

根据上面的实现方式,需要一个开关,根据输入码字“1”或“0”来改变NCO输入频率字,分别输出频率24 MHz与16 MHz。于是设计的MSK调制器如图5所示,前面部分是开关,后面部分是NCO。

图5中clk:时钟采样信号,MSK调制器的开关在其上升沿处数据采样。

clk_sample:时钟信号,NCO时钟采样信号。

data_in:MSK调制器的字符输入端口,其位宽为1b。

reset_n:MSK调制器异步复位控制信号。定义为1表示不进行复位操作,数据有效,MSK调制器正常操作;定义为0表示进行复位操作,数据寄存器清零,MSK调制器清零。

valid:开启MSK调制器的开关。

out:MSK调制器输出端口,其位宽为16b。

outvalid:输出数据的有效位。

3 验证与实现

下面详细叙述采用CycloneⅡ开发板进行编码、组帧、扩频、调制模块的验证结果。

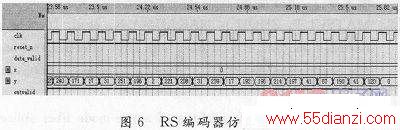

3.1 编码模块的验证

首先验证RS编码模块。采用输入信号为1~223,这223个十进制数。通过Matlab仿真,输出的校正位应该是104,237,65,17,239,22,155,184,61,164,225,240,171,17,31,251,196,2,221,208,31,239,17,192,196,214,197,41,87,190,41,120。QUARTusⅡ测试结果由图6所示。从图中可以看出,设计符合要求。

其次验证交织编码模块。输入数据为上面RS编码器的输出。输出数据为1,17,33,…;2,18,34,…;3,19,35,…;…;16,32,48,…。仿真结果如图7所示。由于数据太长无法显示,只显示部分。

本文关键字:发射机 DSP/FPGA技术,单片机-工控设备 - DSP/FPGA技术