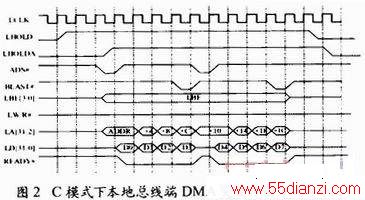

由于PCI9054内部可编程FIFO存储器的存在,数据可以大批量突发传输而不丢失,这样不仪满足实时性要求,同时可以根据用户的需要采用与PCI时钟异步的本地端时钟,PCI9054本地总线工作在C模式时,通过芯片内逻辑控制,将PCI的数据线和地址线分开,很方便地为本地端总线工作时序提供各种方式。图2所示为PCI9054在C模式下与FPGA相连的本地总线数据突发DMA传输方式的时序图,其中,LCCLK为输入时钟信号,从图2中可以看出,在本地端总线上读写数据时,可以不间断地进行突发传输,当数据不能连续传输时,则可以插入等待状态,这样可以大大提高数据的吞吐量。

3 1394b数据传输系统的数据流向

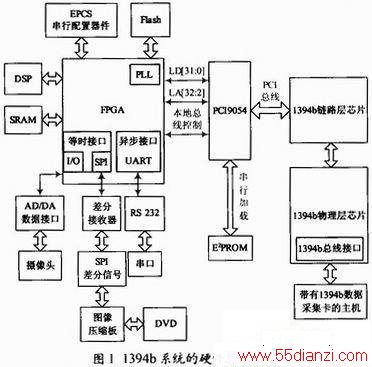

由于1394b总线标准支持等时子事务和异步子事务两类子事务,因此,其传输的数据类型分为等时数据和异步数据,等时传输将数量不定的数据按照规定的时间间隔向某个地址发送,对实时性要求较高,不需要返回确认信号;而异步传输是将数据传送到特定的地址,对数据传输的准确性要求较高,需要接收端以多次握手的方式发送返回确认信号。在本系统中由DVD播放器发送的数据经图像压缩板压缩后由SPI口传入FPGA,或者由摄像头发送的数据经过A/D转换,再由FPGA的通用I/O口送入FPGA,两者均为等时数据;而一些控制命令等异步数据则由串口送入FPGA,并经过DSP进行处理,DSP和FPGA相结合可以提高数据传输的效率。FPGA实现数据的串并转换以及数据的拼接并对数据打包成符合1394b协议的数据包类型以及配置数据包的包头信息,经过读/写FIFO并在外部的SRAM进行缓存,通过DMA仲裁模块进行仲裁处理,用DMA这一快速数据传输机制将数据写入PCI9054的FIFO中。PCI9054作为一种桥接芯片,在本地总线和PCI总线之间提供信息传递,通过PCI9054芯片将本地端数据总线标准转换成能被1394b链路层芯片传输的PCI总线数据标准,再通过1394b的链路层芯片实现对等时和异步数据包的地址和信道号的解码、数据校验、数据分析等,最后由物理层芯片通过仲裁逻辑实现对总线的存取,并对本地节点要发送的数据进行编码,由物理层芯片提供的电气和机械接口将数据位发送到与之相连的1394b线缆上去,最终送入接有1394b板卡的主机进行DVD发送的数据解压缩和播放,以便对摄像头发送的视频进行播放以及异步数据的显示等操作。读出的数据则由接有1394b板卡的主机发送,并通过1394b物理层芯片、1394b链路层芯片、FPGA、外部SRAM等进行数据处理,根据数据包类型由相应的端口送出去,在这期间与发送数据相比进行了相反的操作,这样就实现了1394b双向数据传输系统。

FPGA作为整个系统的控制管理模块,主要完成以下任务:

(1)对SPI端口、UART端口和AD/DA端口数据的发送和接收;

(2)将待发送的数据进行串并转换和数据拼接;

(3)将数据进行打包、解包处理并通过SRAM进行数据的缓存;

(4)与PCI9054芯片进行通信,以完成数据的传送。

本系统中DSP的主要功能是:

(1)与PCI9054芯片和1394b链路层芯片通信实现设备的自举和身份的确认;

(2)发送和接收一些控制命令,控制数据的传输;

(3)实现异步数据的发送和接收功能,根据异步请求数据的类型对其进行相应的处理;

(4)为等时传输申请等时信道和带宽,传输后释放所申请的信道和带宽。

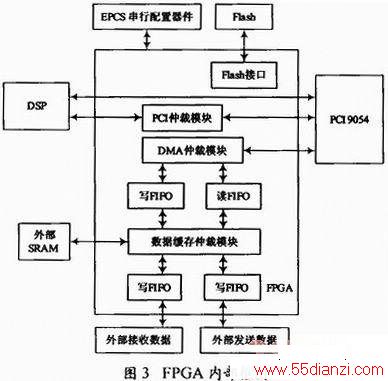

图3所示是系统中FPGA的内部框图,由于数据传输速率较快,数据的处理需要一定的时间,不能将每一组数据无间断的传输,且FPGA内部FIFO容量有限,采用SRAM与FPGA相结合完成输入输出数据的缓存;DSP实现一些辅助的操作如对异步数据的处理、配置PCI9054芯片的内部寄存器和1394b链路层寄存器等操作以及PCI的传输控制、设备识别、为等时传输申请信道和带宽等;EPCS串行配置芯片实现配置数据的存储,使系统上电后将配置数据自动下载到FPGA内部,同时可以用FLASH存储器存放DSP用户代码,在DSP上电工作后,利用DSP提供的boot机制,再将程序下载到DSP RAM中,使本系统实现脱机工作。

4 1394b的系统工作流程

1394b总线的配置是自动进行的,它不受任何设备和主机的干扰。总线配置过程主要有三个步骤:

(1)总线初始化;

(2)自标识;

(3)树标识。

在这三个过程之后,整个系统在逻辑上形成了树状拓扑结构,每个节点都被赋予了一个节点号并都发出节点说明信息。总线的初始化过程如下:

本文关键字:暂无联系方式DSP/FPGA技术,单片机-工控设备 - DSP/FPGA技术