1 前 言

UART 即通用异步收发器,他广泛使用串行数据传输协议。UART 功能包括微处理器接口、用于数据传输的缓冲器(Buffer)、帧产生、奇偶校验、并串转换,用于数据接收的缓冲器、帧产生、奇偶校验、串并转换等。UART的特点是一个字符接一个字符传输,并且传送一个字符总是以起始位开始,以停止位结束,字符之间没有固定的时间间隔要求。每一个字符的前面都有一位起始位(低电平,逻辑值0) , 字符本身由5~ 8 位数据位组成,接着字符后面是一位校验位,最后是停止位(1 位,或1 位半,或2位) , 停止位后面是不定长度的空闲位。停止位和空闲位都规定高电平(逻辑值1) , 这样可以保证起始位开始处有一个下降沿。在一般的使用中往往不需要使用完整的UART功能,比如对于多串口的设备或需要加密通讯的场合使用UART 就不是最合适的。如果设计上用到FPGA ?CPLD器件,那么就可以将所需要的UART 功能集成到FPGA内部,从而使整个设计更加紧凑、稳定、可靠。分析UART的结构,UART 主要由数据总线接口、控制逻辑和状态接口、波特率发生器、发送和接收等部分组成。在本设计中,固定数据帧格式为: 开始位(1 b 低电平)、8 位数据位、偶校验、停止位(1 b 高电平) , 波特率可调。

2 波特率发生模块

设计的UART 的接收和发送按照相同的波特率进行,波特率可以通过接口模块的总线接口进行设置。

UART 收发的每一个数据宽度都是波特率发生器输出的时钟周期的16 倍,即假定当前按照9 600 b?s 进行收发,那么波特率发生器的输出时钟频率应该为9 600×16 Hz.

假定提供的外部时钟为116MHz, 可以很简单地通过总线写入不同的数值到波特率发生器保持寄存器,然后用计数器的方式生成所需要的各种波特率,即分频器。计算公式为: 1 600 000?(16×所期望的波特率) - 1, 如果希望输出10 000 Hz 的波特率,可以得出从总线写入的数值为1 600 000?(16×10 000) - 1= 9 (09H)。

3 发送模块

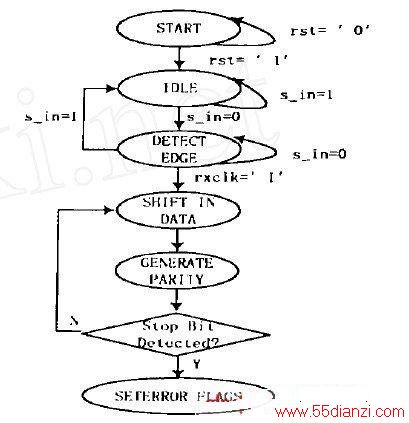

根据UART 协议的描述,发送逻辑流程如图1 所示。

发送数据由接口模块控制,接口模块给出w rn 信号,发送器根据此信号将并行数据锁存,并通过发送保持寄存器和发送移位寄存器发送并行数据。由计数器no_ bs_sent 控制状态的转移,即数据的发送,计数值为1 时,数据从发送保持寄存器传送到发送移位寄存器,计数值为2时,发送开始位(1 b 低电平) , 计数值为3~ 10, 发送8 位数据,计数器为11, 发送校验位,计数值为12, 发送1 位停止位,计数器随后清零。发送时钟是根据数据传输的波特率产生的,16 倍于波特率发生器产生的时钟。

图1 发送逻辑的流程

发送模块信号:

rst (输入) : 复位端口, 低电平有效;

w rn (输入) : 写控制信号;

din [ 0: 7 ] (输入) : 并行数据输入信号;

clk16x (输入) : 外部时钟信号;

tbre (输出) : 发送保持寄存器空信号, 高电平有效;

t sre (输出) : 发送移位寄存器空信号, 高电平有效;

sdo (输出) : 串行数据输出信号。

用VHDL 语言编写代码,使用Xinlinx 的ISE511 进行逻辑综合,运用Modelsim 7.2 做时序仿真,其结果如图2所示。

图2 发送模块时序仿真波形图

4 接收模块

根据UART 的协议描述,可以画出如图3 所示的接收逻辑流程图。接收逻辑首先通过检测输入数据的下降沿来检查起始位,然后产生接收时钟,利用接收时钟来采样串行输入数据,在缓冲器中作移位操作,同时产生校验位,在第9 位处比较校验位是否正确,在第10 位处比较停止位是否为高,在校验位错误或停止位错误的情况下产生错误指示信号。接收时钟是根据数据传输的波特率产生的,16 倍于波特率发生器产生的时钟。

接收模块信号:

rst (输入) : 复位信号;

clk16x (输入) : 输入时钟;

rdn (输入) : 读锁存信号;

rxd (输入) : 串行数据输入信号;

dout [ 0: 7 ] (输出) : 并行数据输出总线;

fram ing_ erro r (输出) : 帧错误信号;

parity_ erro r (输出) : 校验错误信号;

data_ ready (输出) : 数据接收完毕信号。

图3 接收逻辑的流程

运用Modelsim 712 对接收模块做了时序仿真,其结果如图4 所示。接收时钟与发送时钟相同,接收到一帧串行数据,由接收模块转换为并行输出,并且检验校验位和停止位,产生fram ing_ erro r 和parity_ erro r 信号输出。

图4 接收模块时序仿真波形图

5 接口控制模块

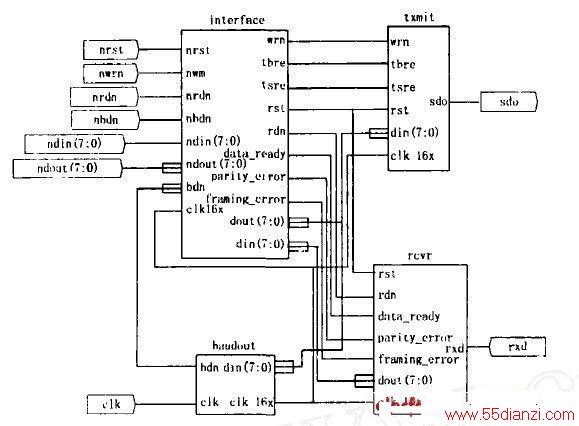

接口控制模块连接控制发送、接收、波特率发生模块,并与外部并行总线相连接,从外部(CPU 或单片机) 接收控制信号(nrst, nw rn, nbdn, nrdn) , 来控制UART 的发送、接收以及内部时钟的生成。在nw rn 有效并且内部信号tbre= ′0′(发送缓冲寄存器空) 时,将数据总线输入的并行数据发送给发送模块数据线din (7: 0) , 执行发送数据功能。在nrdn 有效并且内部信号data_ ready, parity_erro r, fram ing_ erro r 有效时,允许从接收模块读入接收到的数据。波特率发生器和发送模块的并行数据输入端口共用一个数据总线。

6 总体电路综合及仿真

UART 总体电路如图5 所示,分别由上述4 个模块组成。其时序仿真如图6 所示。

图5 UART 总体电路图

图6 UART 总体时序仿真波形图

观察图6, 可以看到串行输出端口sdo 发送一帧数据为“00101011001”, 第一位为起始位,8 位数据位,校验位为“0”(偶校验) , 1 位停止位,空闲状态位为高电平。并行输出端口ndout 输出为“00101010”, 输入数据帧格式正确,校验位正确。

7 结 语

用FPGA 器件实现了UART 异步收发器的核心功能,可以实现对数据的接收和发送,并可以在接收数据时对其校验位、停止位进行判断,在发送数据时可以形成完整的一帧数据格式。其接收和发送数据的时钟有内部波特率发生器产生,根据预置的分频系数,对外部时钟进行分频,产生需要的接收或发送时钟。将该UART 电路作为一功能块嵌入到一个FPGA 实现的数据采集与处理系统中,成功地实现了和远端的PC 机进行异步串行通信。实验证明该UART 电路简单,工作稳定、可靠,可运用于低端的异步通信。

本文关键字:暂无联系方式DSP/FPGA技术,单片机-工控设备 - DSP/FPGA技术