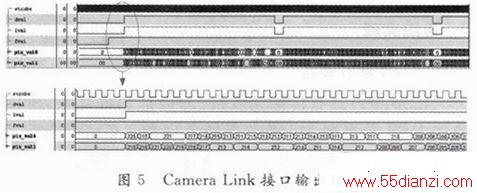

在加载某种8位数据宽度、双通道输出的目标图像时,使用Chipscope得到的Camera Link信号如图5所示。其中,strobe为时钟信号,dval,lval,fval分别是数据有效、行有效、帧有效信号。观测结果说明输出的数据与加载的数据保持一致,输出控制时序也符合要求。

为了模拟出不同类型的CCD相机,只需要修改FPGA程序中设定的strobe时钟频率、Line blanking时间、Frame blanking时间等必要参数即可。

3 实验结果与分析

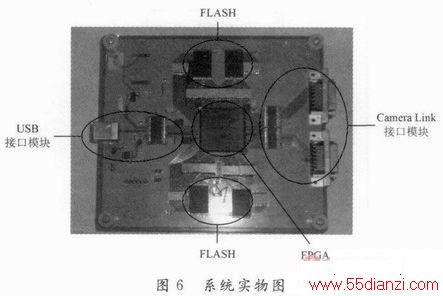

系统实物图如图6所示。

为了检测该信号发生器的性能,将其输出接入图像采集卡进行验证。经过试验验证,FLASH ROM中存储的图像数据与从PC机载入的数据完全一致、控制时序符合设计要求。通过改变Strobe的频率大小,验证得到Camera Link输出的像素时钟频率最大可以达到70 MHz。对于尺寸为128×128、位宽为8 b的目标图像,在采用40 MHz的Strobe时钟进行单通道输出时,帧频可以达到1 876 f/s。对于尺寸为512×512、位宽为8 b的目标图像,当Strobe时钟为70 MHz,单通道输出时,帧频可以达到252 f/s;双通道输出时,帧频可以达到476 f/s。该信号发生器可以模拟目前大部分波前处理机所需的信号源。在进行单通道或双通道输出时,系统可以充分利用Camera Link接口的输出能力。但是当进行更多通道的输出时,由于受限于FLASH的读出速率,该系统不能充分应用Camera Link接口的输出能力。对于这个缺陷,在对系统进行改进时可以通过使用FLASH ROM和高速大容量RAM共同组成数据存储模块来解决。

4 结论

根据本文介绍的设计方案,采用FPGA技术设计的图像信号发生器结构简单,实现方便,易于修改。FLASH ROM提供了较高的数据读出速率,支持系统能够模拟出较高帧频的CCD相机输出。经过试验验证,系统工作稳定,达到了设计要求。