对于网络性能,在 DRAFT 连接 8 个32 位字宽、缓冲深度为 4 个字,频率为100MHz 的组件的配置下,片上网络可使每个连接的组件的最大数据速率高达 1,040Mbps。网络的拓扑和路由协议保证不会出现争用和拥堵现象。在两个互连的组件间,至少一直保留着一条通信路径。数据通过 DRAFT 的平均时延接近 45 个时钟周期(450 纳秒),这符合许多应用的要求。

5 结语

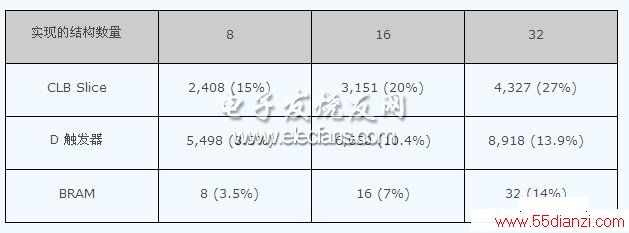

我们提议采用一种创新型的操作系统,可以在由多个处理器和动态可重配置硬件 IP 模块构成的异构多核架构上提供基于多线程的同构执行模型。硬件操作系统负责管理硬件线程,一般用于线程创建和抑制,以及信息量和消息队列服务。在通信方面,我们建议改进用于数据交换的胖树拓扑片上网络、用于硬件线程管理的专用总线以及为实现操作系统间同步的通信层。

本文关键字:动态 DSP/FPGA技术,单片机-工控设备 - DSP/FPGA技术