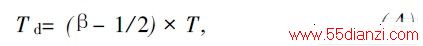

如果不考虑虚警概率的影响,平均确认失帧时间为:

式( 4) 中,β为后向保护参数,即在连续β次发现同步字丢失后才进入失步状态。取β = 3,那么Td= 25 ms。另外,平均失帧时间为:

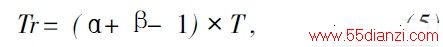

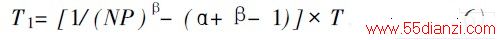

式( 5) 中,a为前向保护参数,即在连续a次找到同步字后才进入同步状态。a= 3,那么Tr = 50 ms。而平均同步持续时间为:

所以T1= 1 607 h。从上面的分析中可以看出复分接系统即使在不进行误码保护的情况下,也能在较短的时间内确认失帧,并很快搜捕到同步; 同时在同步状态保持很长的时间。因此,该复分接系统具有较好的同步性能,在一定的误码保护措施下能够满足实际要求。

3 结束语

设计的数字复接系统的各个部分,都可以在FPGA 芯片上用VHDL 编程实现。整个复分接系统功能就可以集成在一块芯片上,既节省了硬件资源,减少外部走线,简化了系统,而且该设计便于扩展,方便反复编写和修改程序,只需修改FPGA 中相应控制参数和外接的监控信息就可以实现速率可变和帧结构可变的复接与分接。实验表明,该系统在FDMA 便携式卫星传输平台中起到了重要作用,可提高信道的利用率和传输容量。

本文关键字:暂无联系方式DSP/FPGA技术,单片机-工控设备 - DSP/FPGA技术