摘要:为了实现烟支剔除的自动化程度,减少人为干预量和提高剔除精度,文中给出了采用FPGA硬件编程方法将数据采集部件采集到的烟支数据经A/D转换后送入FPGA,然后根据一定的判决算法输出控制信号,以用于控制剔除阀动作,同时将数据通过计算机串口读入上位机,以此实现机械剔除控制和显示实现方法。

关键词:FPGA;烟支检测;数据处理;问题烟;剔除

0 引言

烟支在生产过程中,由于多种因素的影响,可能会使成品烟的烟丝填充不均匀,烟支的某节烟丝过少或过多,从而出现空头烟、超重烟、超轻烟。本系统采用可编程器件控制烟支检测,该方法较其他单独硬件设计具有可重用性高,编程方便,设计成本低,开发周期短,控制灵活,剔除率高等优点;再者,现在的烟支剔除大部分都是人工挑选,故存在工人工作量大,挑选不干净等问题,而该系统可使问题烟的判别、剔除工作自动进行,可对问题烟进行挑选,并能够剔除问题烟。

1 硬件设计

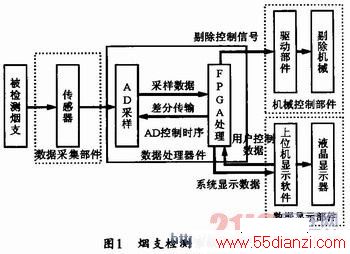

烟支检测系统是用于检测烟支某些参数(如空头烟、重量、密度等)的一个系统,该系统一般可由数据采集(传感器)部件、数据处理部件、数据显示部件、机械控制部件等几个部分构成。其系统框图如图1所示。

其中数据采集部件是系统与被检测参数最直接接触的部分,它是整个系统的数据来源。后期处理是否跟实际一致,直接跟它相关。一般对应不同的物理量,应选择不同的传感器,如空头烟检测可选择光电探头或电容式探头,重量控制可选择重量传感器,密度控制则应选择密度传感器。

数据处理部件是整个系统的核心,传感器采集的数据主要送往该部件进行处理。它一般可由A/D采样板,差分传输板,FPGA处理主板组成。传感器一般得到的数据是模拟量,故应将数据送到数字处理系统进行处理,以将其转化成数字量来进行后期处理。为了保证传输的正确性和可靠性,在A/D采样板送出数据到系统主板之间应使用双绞线差分传输。系统主板主要是以FPGA为核心的控制板,可实现数据处理(剔除)算法,并为后面的机械部分提供控制信号以及将采集和运算数据送到显示器进行显示,从而满足系统设计的要求。

数据显示部件也称为人机交互接口,该部件是整个系统的最直观的表现。它是用户跟系统进行交互的主要部分,用户可以在其上面选择一些阈值和处理方法等参数,也可以控制系统的启动和停止。同时,系统再将一些重要数据显示出来,使用户能够直观得出该系统的工作状况等参数。

机械控制部件是整个系统动作的执行者,因为系统板内部都是弱电,不能驱动机械部件动作,故在其中间需加驱动电路,以使其能够正常工作。其工作主要是当数据处理部件根据一定的判决算法得到某烟为问题烟时,对这些问题烟进行剔除。从而使系统能够自动的检测出问题烟并控制剔除动作,减少人工的干预量,达到自动化的目标。

www.55dianzi.com

2 器件选型

2.1 数据采集部件(探头)的选择

数据采集部件一般位于整个系统的最前端,它的选型对系统的稳定性、可行性有很大影响,本系统选择光电传感器作为探头来对烟支的数据进行采集,它的灵敏度直接与剔除率有关。为了让剔除效果达到最好,探头灵敏度必须调整到合适的设置值。

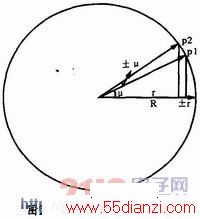

灵敏度包括静态灵敏度和动态灵敏度两种,静态灵敏度主要是在静态情况下探头的光反射强度与探头距烟头的距离、日光、烟头密度及探头电压等之间的关系;动态灵敏度是动态情况下的性能指标。本系统是让探头工作在不同的灵敏度下分析剔除率和误剔率,从而选定剔除性能最好的灵敏度器件。动态灵敏度的另一个影响因素为动态位置误差,即在采样时间内,由轮盘(与轴编码器同步)转动造成的位置变化所引起的探头误差,这里主要从位置误差和探头作用距离上比较,图2所示是动态位置误差示意图。

在图2中,R表示推烟板曲轴的轮盘半径,一次采样过程的起点为p1,结束位置为p2,该段持续时间内的曲轴误差为δr,其中:

若所选A/D采样速率为50kHz,采样周期为2×15-5s,那么,按每分钟400转计算,一次采样时间内的轮盘转动弧度为:

取采样10次的平均,其位置误差不到4μm。而根据探头的位置响应曲线,探头的最佳检测距离在离烟2~3.5mm处,2mm>>4μm,所以,理想情况下由动态位置引起的误差可忽略不计。

根据以上分析,本设计选用韩国KODENSHI公司的SG-2BC传感器。

2.2 A/D转换器的选择

ADS7841E是 德州仪器 公司开发的一块4通道,12位,带串行接口的模数转换芯片,它是一块低功耗、高速度、高精确度的A/D采样芯片,电压为2.7~5 V,可达到200kHz的转换速率。根据笔者对探头的测试,探头检测的最小变化为0.5V左右,而A/D采样的分辨率为3.3/212V≈8×10-4V,所以,该AD采样芯片完全可以满足设计要求。

2.3 FPGA的选择

该系统采用EP3C16Q型FPGA进行控制逻辑编程。该器件是ALXERA公司生产的CycloneII系列高性能现场可编程门阵列,而且具有丰富的逻辑资源。EP3C16Q具有15408个逻辑单元、56个嵌入式乘法器和4个锁相环(PLL),其内部的RAM容量为504Kbits,系统频率高达260MHz,而且稳定性很高。采用单片FPGA实现逻辑控制和数据处理功能可以简化电路设计,提高系统的可靠性并节约成本。设计时,只需一根下载电缆连接到目标板上,就可以多次重复编程,而且电路调试十分方便。

www.55dianzi.com

3 软件设计

本系统的核心处理程序可采用QUARTUSII7.2软件和Verilog HDL语言进行编写,而上位机软件则可采用Delphi7软件进行编写,其核心部分是数据处理部件,它主要由A/D采样、差分传输和FPGA数据处理部分构成,为了使系统实现更加方便,且便于控制,选择FPGA对剔除问题烟的算法非常关键。图3所示是整个系统的程序框图。

3.1 A/D采样

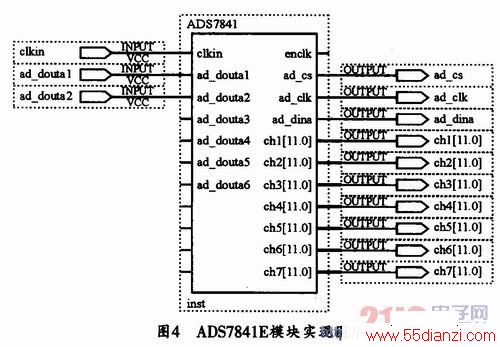

ADS7841E是一款4通道12位的A/D转换芯片,它是由时钟控制的串行输入芯片,芯片DIN中的A2、A1、A0位是通道选择位,MODE位是12b-it/8bit转换选择位,本设计选择高精度的12bit转换,SGL/DIF位用于选择是单端转换还是差分转换,本设计选择单端转换。ADS7841E模块的软件设计原理图如图4所示。

图4中,clkin为系统时钟,CH1~CH7为ADS7841E芯片的转换结果并行输出,该数据可送往FPGA进行判决处理。

3.2 FPGA数据的处理

在对FPGA数据进行处理时,可以采用均值剔除算法。所谓均值剔除算法,就是用一个样本的当前值与一个参考值相减,然后取绝对值,如果结果超过某一门限,就说明其不符合要求,故可舍弃这个数据。假设随机变量X具有数学期望μ和方差σ2,那么,对于任意正数&epSILon;,其不等式(6)成立:

![]()

不等式(6)称为切比雪夫不等式,若令ε=3σ,则可得到:

其中,μ为正态分布的期望,σ为正态分布的均方差。由式(8)可知,对于正态随机变量来说,它的值落在区间[μ-3σ,μ+3σ]内几乎是必然的事件,这就是3σ规则。

本文关键字:检测 DSP/FPGA技术,单片机-工控设备 - DSP/FPGA技术

上一篇:多通道频率检测技术的FPGA实现