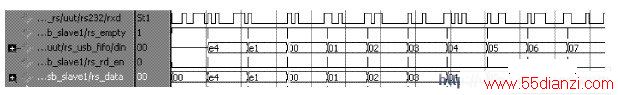

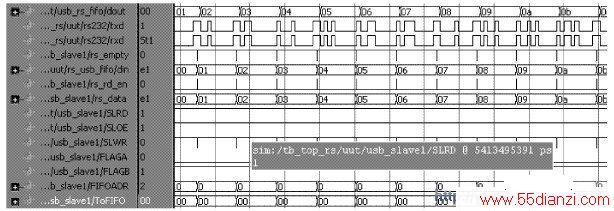

图5 为RS 232 与FPGA 接口部分仿真结果。可以看出, 由RS 232 接收串行数据RXD 已经转换为并行数据din。程序中是在一个有效字节结束后将其存入FIFO 中, 由图可以验证。图6 顶层模块仿真图, 为了验证由FPGA 发出的数据能正确的接受到, 先由FPGA 内部发数据, 然后通过RS 232 的T XD 端口发出,让RXD 与TXD 相连再接收, 可以看出发出的数据可以被正确的接收回来并传向U SB 接口, 说明时序正确。

同理可以验证U SB 端的收发时序。

图5 RS 232 接收端仿真图

图6 顶层模块仿真图

4 结 语

本文采用FPGA 实现了USB 与RS 232 间的接口转换及数据处理的功能。设计中先入先出存储器的运用解决了数据的缓存的和速率匹配问题, 有限状态机的运用使得程序设计更加清晰可靠。该设计将复杂的信号运算集中在FPGA 中完成, 利用FPGA 独特的并行处理能力,减小上位机工作量的同时, 提高了系统运行速度。