摘要:经典的码盘数字测速方法有M法、T法、M/T法,但都有一定的不足。为了克服原有方法的不足,设计并实现了一种在较大速度范围都有良好精度和良好快速性的测速方法。电路采用FPGA实现,测速得到的数据通过PCI总线从设备控制器实现与控制计算机通信。从而根据实际传输的需要,简化了PCI从设备控制器,实现了PCI总线I/O普通读与猝发读数据的功能。

关键词:测速;FPGA;PCI;M/T

O 引言

增量式码盘是一种原理简单,抗干扰能力强,可靠性高,适合于长距离传输的位置与速度测量装置,已成功应用于大量的控制系统中,极大地提高了其位置控制精度。理论上,只要测得码盘输出信号的频率,即可得到被测轴的转速,并且可以得到比模拟方法更高的测量精度。本文以增量式码盘为基础,设计实现一种在较宽速度范围都有较高精度并且有良好反应速度的速度、位置测量装置。

利用增量式码盘的反馈脉冲信号测量速度的典型方法有3种:M法、T法和M/T法。其中,M法是直接计取给定采样周期内的反馈脉冲数来测量速度的,低速时会因为脉冲数少而影响测速精度;T法是通过测量两个相邻反馈脉冲的间隔时间来测量速度的,高速时则因为脉冲间隔短而导致精度不高;M/T法结合了前两种方法的优点,在大致相等的采样间隔内,计取Cm个反馈脉冲,并同时计取这Cm个反馈脉冲间隔内插入的高频时标信号数Cf,经计算得到速度测量值。M/T法虽然克服了前两种方法的缺点,但仍存在低速时采样时机不确定,精度不高等问题,这给定周期采样的数字伺服控制系统带来很大的不便,所以又出现了变M/T法等方法,以进一步改善M/T法的性能和实用性。

本文利用FPGA实现了一种改进的M/T法,克服经典M/T法的不足,其测速电路与控制器间的数据接口形式有PCI总线和双端口RAM,便于在高性能控制系统中使用。

1 总体方案

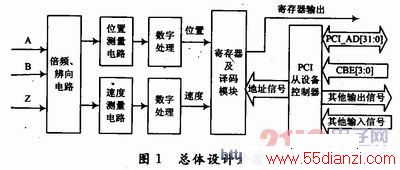

根据控制系统的实际情况,所设计的测速板具有位置测量和速度测量功能,如图1所示,由倍频辨向模块、改进M/T法测速模块、PCI从设备控制器三个部分组成。

1.1 倍频辨向

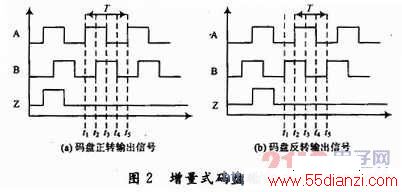

增量式码盘的典型输出是两个相位差为90°的方波信号A,B以及零位脉冲信号Z(见图2)。

A,B之间的相位关系标志被测轴的转向,即当正转时A相超前B相90°,反转时B相超前A相90°。对于每个确定的码盘,其脉冲周期T对应的码盘角位移固定为θ,故其量化误差为θ/2。如果能将A,B信号四倍频,则计数脉冲的周期将减小到T/4,量化误差下降为θ/8,从而使增量式码盘的角位移测量精度提高4倍。从图2可知,根据A,B两方波信号之间相位关系的4次变化,即可产生四倍频信号和辨向信号,这样就可以实现增量式码盘测量精度的提高。

www.55dianzi.com

1.2 改进的M/T测速算法

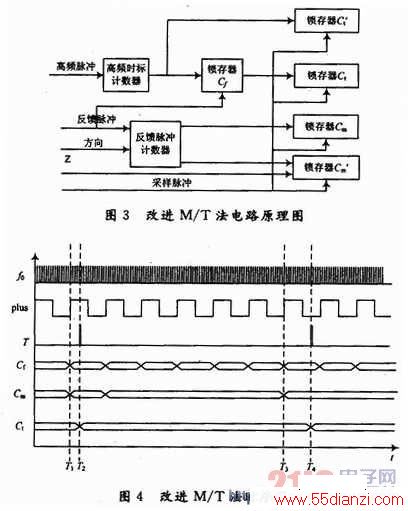

图3展示了改进M/T法的电路原理,这是实现高精度的硬件基础。图4为改进M/T法的时序图。

对图3及其时序图4的分析可以看出:本测速电路在每个反馈脉冲时锁存高频时钟的计数值,两个采样周期间的高频时标增量值Ct实际表示为T2前一个反馈脉冲上升沿到T4前一个反馈脉冲上升沿的高频时标增量,而在采样周期内每个反馈脉冲到来都对反馈脉冲计数器计数,两个采样脉冲采得反馈脉冲增量值Cm实际表示为T1~T3之间的反馈脉冲增量值,位置的反馈脉冲增量值则是在Cm的基础上考虑方向得到的,那么结合32位浮点运算,这种测速方法就解决了采样时机不确定的缺点。

根据上述分析,通过差分处理就可得到当前实际采样间隔内的反馈脉冲增量值Cm和高频时标增量值Ct:

![]()

这样得到的速度是当前实际采样间隔内的平均速度:

![]()

式中:KR为反馈信号脉冲当量;fo为高频时标频率。

在实际采样点T2处,高频时标信号fo的边沿不能总与反馈脉冲信号plus的边沿保持一致,因而会产生±1个高频时标当量的计数误差,从而影响这种测速算法的测速精度。因此高精度数字测速算法的测速相对误差为:

![]()

动态位置算法不仅关注已经发生的反馈脉冲数量,也关注反馈脉冲的发生时刻,其硬件基础是依据图3所示逻辑电路的。根据当前有效采样周期的定周期采样点和实际采样点之间的时间差:

![]()

并根据改进的M/T法得到被测对象的平均速度vn,由vn和△Tn相乘就可以计算出时间差△T(n)中所包含的动态位置信息,因此由当前有效采样周期内的增量式高精度动态位置信息可以得出位置量:

![]()

可根据这种方法完成测位置的功能。

www.55dianzi.com

2 各个模块VHDL实现

根据图1的总体设计方案,使用VHDL语言设计实现如下几个模块。

2.1 倍频辨向模块

为便于使用VHDL语言描述,对图2的码盘信号作如下分析:

(1)当码盘正转时,在一个周期T内,A,B两相信号共有4次相对变化:00→1O→11→01。这样,根据前一次和当前的信号,就可以判断方向,并产生四倍频脉冲。

(2)同理当码盘反转时,也根据A,B两相信号的4次相对变化:00→01→11→10,可以判断方向,并产生四倍频脉冲信号。

(3)当线路受到干扰或出现故障时,则可能出现其他状态转换过程,此时不产生脉冲。

根据上述分析就可以设计出测速辨向模块,当判断正转时,把方向输出置‘1’,反向时置‘O’。

2.2 改进M/T法测速模块

如图3所示可以看出,本部分的VHDL设计分成两个模块:计数器模块与锁存器模块。

其中,计数器模块分为两种:高频时标计数器和反馈脉冲计数器。高频时标计数器在每个高频时标的上升沿都做+1计数,在每个反馈脉冲的上升沿对计数值锁存。反馈脉冲计数器,需要两个输出:反馈脉冲计数值Cm、位置反馈脉冲计数值。其中,Cm的增量值用于速度的计算,所以在每一个反馈脉冲到来时,计数器都+1;的计数值用于位置的计算,所以它是在Cm的基础上考虑了码盘方向得到的计数值,在正转时反馈脉冲计数器+1,反转时-1,当零位脉冲Z有效时,对其置0。然后分别输出Cm,,由此就可以得到反馈脉冲计数器模块。

在每个采样周期的上升沿还要锁存Cm,Ct的增量值和与Ct的差值,由于都做了差分处理,所以这三个锁存器使用双字就能满足设计要求,而锁存器在零位信号Z后不进行差分处理,若采用36 000刻增量式码盘,并进行10 000倍频,位置范围为±720°,那么需要的最大计数值为:

(36 000×10 000×720×2)/360=1 440 000 000

可见,双字锁存器也能满足设计要求。

综上所述,本设计设置了4个双字信号锁存器Cm,,Ct,,同时还需要对其控制输出,所以在PCI从设备控制器中为I/O分配4个双字的地址空间。然后根据PCI总线给出的地址信号PCI_AD[3:2]和数据输出使能信号DATA_EN对这4个双字寄存器寻址输出。

2.3 PCI接口控制器

PCI的时序规则和PCI的总线协议由PCI接口控制器实现,同时它还负责传递地址和数据输出使能信号给测速模块,实现I/O口的基本读与猝发读数据功能。

本文关键字:暂无联系方式DSP/FPGA技术,单片机-工控设备 - DSP/FPGA技术