3 TMS320C2407A/TMS320VC33与CY7C025之间通信的实现

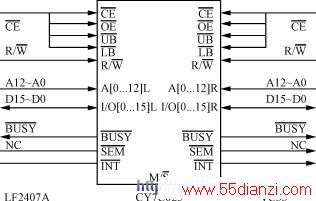

LF2407A的数据总线宽度和地址总线宽度都是16位,单片CY7C025就足够了。VC33的数据总线宽度是32位,可以采用两片CY7C025以主从模式进行宽度扩展(见图3),这样每次VC33读取数据时就能一次读入两个LF2407A的采样数据。也可以采用单片CY7C025,虽然没有完全利用VC33的数据宽度,但是,从电路设计上来讲相对简洁。由于本系统双口RAM的作用主要是起到数据传递的作用,不需要保存大量的中间结果以及已经使用过的数据,因此,需要的存储空间不是很大,单片双口RAM就已经足够。具体的接口电路见图3,片选等控制信号由译码电路产生。

图3 接口电路实现

地址空间分配综合了不同DSP的空间资源分配要求,具体见表1。

表1 地址空间分配表 起始地址 终止地址 LF2407A 0X8000H 0X9FFFH VC33 010000H 011FFFH

4 软件功能实现

双DSP协同工作的关键是相互通信和数据交流上的密切配合,可通过硬件仲裁电路来完成这一任务。但是如果仅仅用硬件完成,如上分析,毕竟等待时间还要0.4μs左右。如果辅以软件配合,则可以有效地减少等待产生的情况。

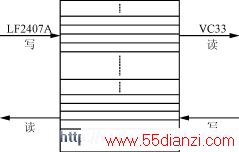

首先,冲突可能发生在同时写同一个存储单元。在数据写的时候采用如下措施可以避免这种情况的发生:如图4所示,将读/写的存储空间独立开来,显然LF2407A和VC33在写的时候就不可能产生冲突,避免了等待的发生。

图4 读/写存储空间分开

其次,冲突可能发生在一读一写同一存储单元的情况下。以LF2407A写数据,VC33读数据为例,上面分析的产生0.4μs等待时间的情况是基于如下假设:将8个数据依顺序存储于同一地址单元。即LF2407A存第一个数据时发生冲突,VC33产生等待时间50ns,等待结束VC33读数据,此后LF2407A将第二个数据覆盖前一个数据存储,依次类推得出的结果就是8×50ns=400ns。事实是我们有足够的地址空间用来存储每批数据,将8个数据按顺序存放在不同的地址空间,此时的情况如下:LF2407A存第一个数据时发生冲突,VC33产生等待时间50ns,等待结束VC33读数据,与此同时LF2407A也开始写第二个数据于下一个存储单元中。两者同时进行,我们只要保证VC33读完的时候,LF2407A第二个数据已经写完,则不会有冲突发生。针对本例,由于两者时间不同(LF2407A为50ns,VC33为13.3ns),VC33读得较快,只要在软件编写上增加40ns左右的循环,就能保证如上的要求。当读/写反过来的时候,则不存在这样的情况而能顺利配合。这样,最终的结果是只增加50ns的等待周期,对于本系统完全可以接受。

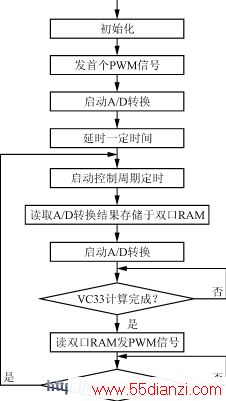

由于两个DSP并不同步工作,所以,LF2407A可以采样尽可能多的数据并保存,VC33只选用最新的数据用于计算,这样就能保证数据的冗余。程序流程如图5所示。

(a)LF2407A流程图

www.55dianzi.com

(b)VC33流程图

图5 利用双口RAM进行双机通信流程图

5 结语

双DSP控制系统综合利用了TMS320LF2407A和TMS320VC33芯片的优势和特长,两者在控制和计算上分工明确,并行工作。利用双口RAM实现数据和信息的交流的时候,针对电机控制系统采样数据相对较少的特点,从硬件和软件上相互配合,在解决存储空间争用的同时,很好地解决了等待时间等资源的浪费,也避免了数据交换时利用中断造成的软件不稳定。实现了两者之间的协调工作,大大缩短了控制周期,提高了控制平台的性能。对于低电感同步电机直接转矩控制时,由于控制周期过长而引起电流上升过大的问题能很好地加以解决,同时也使转矩脉动明显减小。

本文关键字:电机 DSP/FPGA技术,单片机-工控设备 - DSP/FPGA技术