DS/FH混合扩频通信系统中,需要数字下 变频器 、相关累加器及码发生器等完成下变频、相关解扩等运算。通常采用专用芯片来完成这些功能,导致系统体积增大不便于小型化。现代的EDA(电子设计自动化)工具已突破了早期仅能进行PCB版图设计或电路功能模拟、纯软件范围的局限,以最终实现可靠的硬件系统为目标,配备了系统自动设计的全部工具,如各种常用的硬件描述语言平台VHDL、Verilog HDL、AHDL等;配置了多种能兼容和混合使用的逻辑描述输入工具,如硬件描述语言文本输入法(其中包括布尔方程描述方式、原理图描述方式、状态图描述方式等)以及原理图输入法、波形输入法等;同时还配置了高性能的逻辑综合、优化和仿真模拟工具。 FPGA 是在PAL、GAL等逻辑器件的基础上发展起来的。与PAL、GAL等相比较,FPGA的规模大,更适合于时序、组合等逻辑电路应用场合,它可以替代几十甚至上百块通用IC芯片。FPGA具有可编程性和设计方案容易改动等特点,芯片内部硬件连接关系的描述可以存放在下载芯片中,因而在可编程门阵列芯片及外围电路保持不动的情况下,更换下载芯片,就能实现新的功能。FPGA芯片及其开发系统问世不久,就受到世界范围内电子工程设计人员的广泛关注和普遍欢迎[1~5]。本文主要讨论一种基于编码扩频的DS/FH混合 扩频接收机 解扩及同步过程的实现结构,采用ALTERA公司的APEX20K200RC240-1器件及其开发平台QUARTus II实现混合扩频接收机的核心--解扩及同步模块。

1 混合扩频接收机解扩模块的FPAG设计

解扩模块是混合扩频接收机的核心。该模块实现对接收信号的解扩处理,主要包括数字下变频器、数控振荡器(NCO)、码发生器、相关累加器和伪码移相电路等,通常各模块采用专用芯片。利用FPGA将这些功能集成在一块芯片中,大大缩小了接收机的体积,便于实现系统的小型化和集成化。下面分别介绍该模块各部分的FPGA实现结构。

1.1 数控振荡器(NCO)

数控振荡器是解扩模块中的重要组成部分,主要用于为码发生器提供精确的时钟信号,从而实现对接收信号的捕获和跟踪。码发生器由相位累加器和查找表构成。若使用字长为40位宽的累加器,对于某一频率控制字A,输出频率fout与输入频率控制字A的关系为:

fout=fclkA/240

其中,fclk为系统时钟。只要改变控制字A的大小,就可以控制输出频率fout。fout变化的最小步长Δf由累加器的数据宽度决定。若数据宽度取40位,则:

Δf=fclk/240

利用上述原理,可以通过精确分频得到所需频率。原理图如图1所示。

图1中频率控制字A由DSP写入。考虑到FPGA内部存储资源限制,取40位相位累加值result[39..0]的高八位作为查找表LUT(look-up table)的输入,查找表由ROM构成,存储各相位所对应采样值。当查找表输入端为某一相位phase时,则输出对应采样值。若输出数据宽度为6位,输出信号格式为余弦信号,则LUT输出为[6]:

out[5..0]=31×cos(360×(phase+0.5)/256)°+32

若取ROM的并行6位out[5..0]作为输出,则输出信号为每周期采样256点的数字化余弦信号;如果取最高位out[5]作为输出,则输出为系统时钟的分频信号。

1.2 数字下变频器

数字下变频器将A/D采样得到的中频信号进行下变频处理,去除中频,得到基带信号。利用本地NCO产生与输入中频信号频率相同的正弦和余弦信号,并与输入信号进行复乘法运算,然后对运算结果做低通滤波,即可完成对中频信号的下变频操作。正交采样模式下,两路A/D转换器提供正交输入IIN及QIN,数字下变频器的复乘法器输出IOUT、QOUT为:

IOUT=IINcos(ωt)-QINsin(ωt)

QOUT=IINsin(ωt)+QINcos(ωt)

本振信号、复乘法器、低通滤波器均采用数字化设计。数字下变频器采用ALTERA公司的APEX20K200RC240-1器件。该器件典型门数为20万,有丰富的逻辑单元和RAM单元,开发平台Quartus II 自带的宏模块,如lpm_mult(乘法器宏模块)、lpm_rom(ROM宏模块)、lpm_add_sub(加法器宏模块)等,给设计带来了极大的方便。数字下变频器原理图如图2所示。

图2中的数字表示相应模块的数据宽度。滤波模块是1个二阶的低通滤波器,滤除混频后的高频分量。在一些专用的数字下变频器件如STEL-2130中,滤波器的阶数是可编程的,可以根据需要设置不同的阶数,从而得到不同的滤波效果。考虑到FPGA的资源问题,设置滤波器的阶数为固定的二阶。滤波器输入x[n]与输出y[n]关系为:

y[n]=x[n]+x[n-1]

y[n-1]=x[n-2]+x[n-3]

该低通滤波器将相邻的两个输入数据相加后作为输出,即每两个输入数据对应一个输出数据,输入数据时钟节拍为输出数据时钟节拍的2倍。

经过低通滤波后的数据经过滑动窗处理,滑动窗对输入数据进行选择输出,用来动态调整相关峰的大小。在捕获过程中观察相关峰值时,通过调整滑动窗口,可以获得不同幅度的相关峰值。选择控制端由DSP写控制字来决定,结构如图3所示。滑动窗控制逻辑关系为:

CASE sel[] IS

WHEN 0=> dataout =datain[7..0];

WHEN 1=> dataout =datain[8..1];

WHEN 2=> dataout =datain[9..2];

WHEN 3=> dataout =datain[10..3];

WHEN 4=> dataout =datain[11..4];

WHEN 5=> dataout =datain[12..5];

WHEN OTHERS => dataout =datain[12..5];

符号扩展是为了与后面的相关累加器数据宽度保持一致,符号位扩展时需与输入数据最高位的符号保持一致。

1.3 相关累加器

相关累加器完成本地伪码与接收信号的相关累加运算,运算得到的结果送入DSP完成伪码的捕获和跟踪。取伪码长度为256位,采用半码片滑动,则一个码周期完成512次累加运算。如采用串行滑动相关捕获方式,则遍历所有的码相位所需要的时间为512个码周期,即捕获所需要的最长时间为512个PN码周期。由于可编程逻辑器件的发展,使得有足够的硬件资源来完成并行运算。此处采用串/并混合的捕获方式[6][7],采用8路相关累加器,每一路分为超前、当前、滞后3组,每组相差半个码片的相位,每一路相差64个半码片的相位。这样,只需滑动64个半码片相位就可以遍历所有的伪码相位,完成捕获所需时间缩短为原来的八分之一。数据解调由另外4组相关累加器完成。由于发射端同步伪码与数据伪码相位严格对齐,所以在接收模块中,完成同步伪码捕获跟踪后,直接将所获得的相位信息用于数据解调相关器,即可正确解调数据。

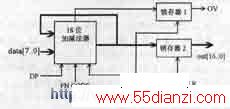

同步伪码的跟踪采用超前-滞后延迟锁相环路( DPLL ),每一路相关器包括3组累加器。捕获跟踪及数据解调共使用28组相关累加器,每一组相关累加器结构都是完全一样的,均分为I、Q两路,分别进行累加运算,完成512次累加运算后由DSP读取数据。I、Q两路结构完全相同,其中一路的原理图如图4所示。

相关累加器由18位加减法器、锁存器1和锁存器2组成,data[7..0]为下变频后的输入数据,PN CODE来自码发生器。作为控制端,低电平完成加运算,高电平完成减运算,DP上升沿进行数据锁存,下降沿完成一次累加运算。当累加运算完成后,由CLR信号清零并将结果存入锁存器2,CLR下降沿有效。锁存器1输出OV信号作为溢出标志位,锁存器2输出累加结果out[16..0]。输入与输出端的最高位为符号位。

1.4 本地码发生器及码移相电路

本地码发生器用于产生本地PN码,从而与接收信号进行相关运算。由于发送端采用编码扩频调制方式,接收信号中既有同步PN码,还有数据PN码,与接收信号相对应,本地也应该产生相应的PN码,用于同步及解调数据。

本地PN码发生器全部采用 FPGA 实现,并且设置了可编程寄存器和外部接口,DSP通过接口可预置PN码长度。1024进制计数器电路用于产生ROM的输入地址,ROM由FPGA内部RAM资源来实现,采用ALTERA公司APEX20K200器件。该器件内部可编程RAM容量为106496位,完全可以满足设计需求。本地PN码采用半码片滑动方式,ROM内部PN码也以半码片方式存储。如码长为256,采用半码片存储方式后,每一组PN码需存储512位数据,相应的ROM有9位地址线驱动输出。驱动时钟为PN码时钟的2倍。在实际设计时,PN码发生器内存放了8组PN码,但只用了五组,一组用于同步,另外四组用于解调数据。ROM输入地址由1024进制计数器产生,实际上只需用512进制计数器即可得到ROM输入地址。考虑到可扩展性,这里采用了计数容量最大为1024的可变计数器。由DSP通过DSP-FPGA接口改写寄存器值,可以很方便地调整PN码的输出相位。

上一篇:基于FPGA的多路视频通道控制