引言

卷积码 是深度空间通信系统和无线通信系统中常用的一种差错控制编码。在编码过程中,卷积码充分利用了各码字间的相关性。在与分组码同样的码率和设备复杂性的条件下,无论从理论上还是从实践上都证明,卷积码的性能都比分组码具有优势。而且卷积码在实现最佳译码方面也较分组码容易。因此卷积码广泛应用于卫星通信,CDMA数字移动通信等通信系统,是很有前途的一种编码方式。对其进行研究有很大的现实意义。

1 、(2.1.2)卷积码的基本概念

1.1(2.1.2)卷积码的结构图

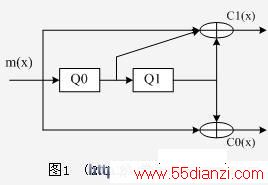

(2.1.2)卷积码的编码器由两级移位寄存器组成,它的存数(Q0,Q1)有四种可能:00,10,01和11,相应于编码器的四个状态S0, S1, S2和S3。(2.1.2)卷积码编码器如图1:

由图可知,该卷积码的生成多项式为

于是,得到的码多项式是

![]()

1.2(2.1.2)卷积码的网格图表示

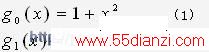

为了表示卷积码编码器在不同输入的信息序列下,编码器各状态之间的转移关系,以及状态转移与时间的关系,须画出编码器的网格图。网格图是一种能清楚显示状态转移的时间依赖性状态图,因而用网格图来表示编码器的操作是很有用的。图2表示了(2.1.2)卷积码的网格图。图中四行小圆圈表示移位寄存器的四种状态,虚线表示输入是0时的状态转移,实线表示输入是1时的状态转移,支路上标注的码元为输出比特。

2 、(2.1.2)卷积码编码器的编程实现与仿真波形

由以上分析可以发现,(2.1.2)编码器由两个模二加法器组成,分别生成 、。而此时输出的是并行数据,须经过并串转换才能输出,在用 VHDL 编程时,用LOAD和CLK来控制信息的输入与卷积码的产生,当LOAD为底电平时,在每个CLK的上升沿输入一位信息,并进行异或运算;当LOAD为高电平时,在CLK的上升沿时刻,把生成的卷积码经过并串转换之后输出。

经过编译调试之后,仿真波形如图3:

图中,D-IN为输入的信息位,D-OUT为输出的串行卷积码,Q为移位寄存器的内容。输入序列为:1 0 1 0 1 0 … …,输出为:11 10 00 01 10 … …。实现了编码器的功能。

3 、(2.1.2)卷积码 译码器 的编程实现与仿真波形

对接收到的编码序列进行译码时,利用网格图寻找最大可能的输入码序列作为译码输出。维特比译码算法通过限制搜索的序列数目简化了译码过程,对每个新输入的符号只保留转移到各个状态的最可能路经。

实际译码过程中,考虑到译码延时与译码器存储量,常采用截尾译码方式。即在处理完第L段码元序列后,译码器就开始输出第1个判决比特,L称为译码深度,等于译码器的译码输出延时。理论表明,当L=5~10v时(v为卷积码编码存贮长度),对译码器输出的译码错误可以忽略。本方案采用L=6v。

3.1 卷积码译码器的程序设计

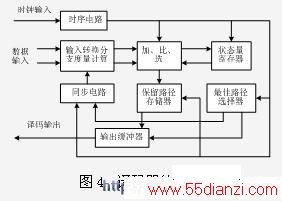

(2.1.2)卷积码译码程序总体结构分为六个模块,分别实现接收序列的读入、四个状态的“加、比、选”运算、维特比的回溯输出等功能。译码器的结构方框图如图4:

(1)接收码元输入和记数部分。

这部分用来实现接收序列的读入,并对其进行串并转换。用CLK和LOAD来控制,当LOAD为底电平时,在每个CLK的上升沿输入一位信息,每次输入两位信息。同时,记数器加2。

本方案采用的译码深度为6v,即12。引入一个计数器,当计数达到要求时,控制译码器开始输出译码序列。仿真波形如图5:

(2)“加、比、选”运算部分。

似然序列估计的维特比译码算法,关键技术就是“加、比、选”。(2.1.2)卷积码共有四种状态,每个状态都必须进行以上运算,须用四个模块来分别实现S0,S1,S2,S3的“加、比、选”算法。下面仅以状态S0为例来详细介绍此算法。

如图2的网格图所示,图中从前级每个节点上都有2条支路延伸到下一级,而下一级上的每2条支路又都汇聚在一个节点上。对于状态S0,它向状态S0、S1转移,而状态S0和S2向它汇聚。因此S0把汇聚在它的节点上的偶奇两个老状态S0和S2的度量读出,分别加上本地编码与接收码元的差值(距离),比较两个和值的大小,选择度量较小者作为新状态的度量。因为本卷积码的译码深度为12,所以给该状态配备一个12位的移位寄存器,用于记录每次运算后所得到的相应的路径,以备后面的回溯译码。此处理过程可简称为“加、比、选”。

(3) 卷积码 的回溯译码输出部分。

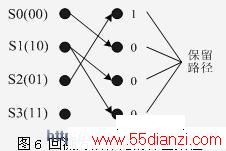

图6示意了回溯译码的基本思想。每次节点处理器并不传递幸存路径寄存器的内容,而是给每个节点处理器分配一个独一无二的寄存器,其中保存了该节点处理器挑出作为幸存路径的状态的最低位比特。对于图中选择的幸存路径,节点处理器对状态“00”存“1”(因为它选择来自状态“01”的路径),而其他每个处理器因为其路径选择都存“0”。

本方案采用了回溯的译码方法,现将具体的译码方案介绍如下;

当计数器DJ所累加的数目达到要求时,此时译码输出模块开始工作。程序首先判断四种状态的路径度量,选出最小的路径度量,并将此状态作为回溯的初始状态。开始回溯译码。由于本方案的译码深度为12,这就要求每输出一位译码,必须向前回溯12位。这在实际运用很不适用。因此,增加了一个输入脉冲,其频率是主脉冲CLK的6倍。这样,在不影响以上程序正常运行的情况下,保证了译码的及时输出。

3.2 卷积码 译码器 的仿真波形

图7为输入一串正确的卷积码的译码波形图,图中,输入的卷积码序列为:11 10 00 01 10 01 11 11 10 … …,输出的译码序列为:1 0 1 1 1 0 0 1 0 0 … …。实现了正确译码功能。

图8为输入一串有误码的卷积码的译码波形图,输入的卷积码序列为:0(1)1 10 00 01 10 01 0(1)1 11 10 … …,输出的译码序列为:1 0 1 1 1 0 0 1 0 0 … …。也实现了正确的译码功能,这表明本方案设计的卷积码译码器完全能够符合卷积码译码的要求。当然,如果差错出现太频繁,以至超出卷积码的纠错能力,则会发生误纠。

4 、结论

本设计选择的(2、1、2)卷积码,是极具代表性的卷积码。因为卷积码具有相似的结构和特点,所以(2、1、2)卷积码的编/译码设计思想,对所有的卷积码都是适用的。为了便于修改理解,该编/译码器的设计采用了模块化的设计方式。在设计过程中,重点解决了译码过程中状态度量的计算,转移路径的选取,保留路径的存储和译码的回溯输出。最后的仿真结果显示,编译码的效果比较理想。达到了设计的目的。

本文关键字:译码器 DSP/FPGA技术,单片机-工控设备 - DSP/FPGA技术