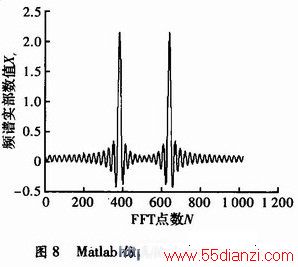

通过比较可以看到,本设计的仿真结果与Matlab的仿真结果基本一致,可以正确高效地计算出1 024点FFT数据。

3 结束语

本设计全部由Verilog HDL语言实现,采用自顶向下的设计方法,完成了一种基于 FPGA 的1 024点16位 FFT算法 ,共需要5级运算,每级需要计算256个蝶形。提出了将蝶形运算先进行前一级的蝶形加减运算,再进行本级的与旋转因子复乘运算的结构。由前所述,平均每个蝶形运算需要4个时钟周期,所以理论上完成1 024点FFT的总时钟周期为N=256×4×5=5 120;假设使用的时钟为100MHz,那么将耗时T=5 120×(1/100)=51.2μs,这与仿真结果51.32μs基本一致。

本文关键字:硬件 DSP/FPGA技术,单片机-工控设备 - DSP/FPGA技术