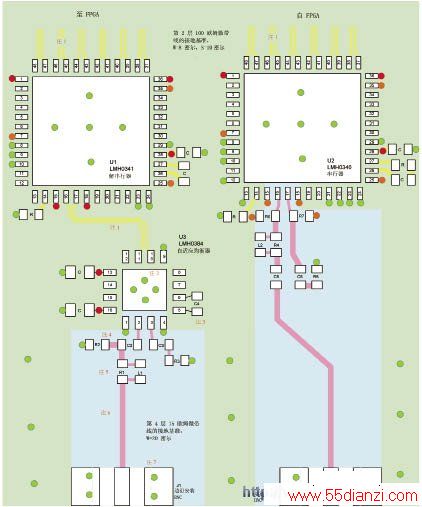

图9 LMH0384、LMH0340和LMH0341的布局示例

交流耦合电容器C2紧邻SDI+的输入针脚。阻抗匹配网络L1和R1通过C2尽可能地靠近输入针脚SDI+。75Ω终端电阻器R2置于C2后方,以最大限度减小接线柱的影响。

这种设计使用0402尺寸元件,尽可能减少75Ω迹线的阻抗变化,75Ω迹线通过20密尔微带线连接到第4层基准。BNC使用的布局应具有良好的信号发送,以实现低回波损耗。

图9注释如下:

总结

SDI板布局的难点在于设计一种方案,可以最大限度减少75Ω端口上很多外部元件引起的阻抗失配。使用75Ω微带线以及与无源元件的接合焊盘尺寸相当的迹线宽度可以实现使阻抗失配降到最低的目标。使用第二接地基准就可以为连接到高针脚数FPGA的100Ω差分迹线灵活选择较细迹线宽度。务必使用75Ω受控阻抗设计良好的BNC布局。建议在信号路径上查找因布局结构变化引起的阻抗变化,并设计一种方式可以抵消过多电感或电容以保持目标特征阻抗值。通过遵循几个简单的布局指导原则,可以设计符合SDI高信号保真要求的板,并实现高密度连接至FPGA。

本文关键字:暂无联系方式DSP/FPGA技术,单片机-工控设备 - DSP/FPGA技术