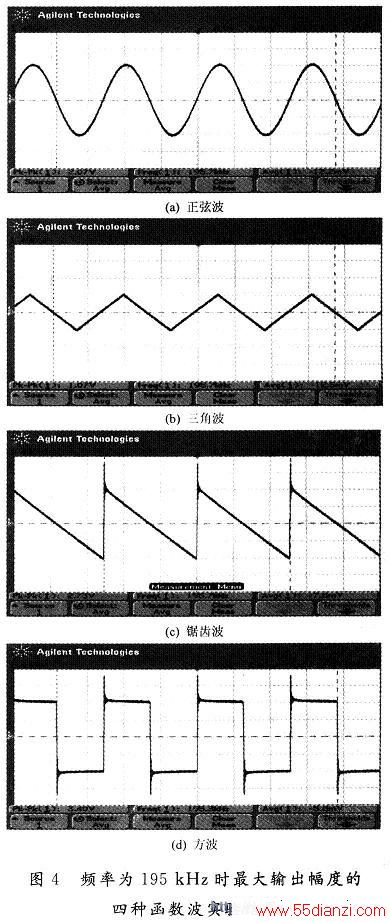

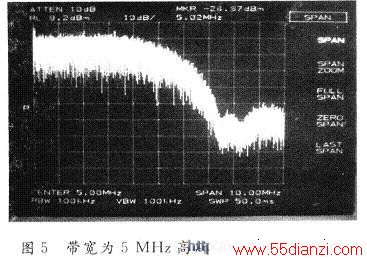

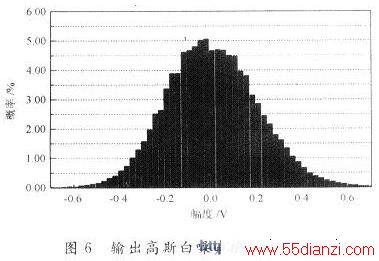

从图4可以看出,采用DDS模块,得到了正弦波、三角波、锯齿波和方波的波形。图5为该噪声和函数波 发生器 产生的5 MHz噪声的实验结果,图6是输出带宽为5 MHz的 高斯 白噪声 统计直方图。

从图5和图6可以看出,基于FPGA的m序列发生算法,FIR滤波算法和DDS算法,通过数/模转换和低通放大后,本文设计的噪声发生器产生的5 MHz噪声的3 dB,带宽为4.8 MHz,带内平坦度为±1.5 dB,输出噪声的统计特性服从高斯分布,满足了设计需要。

4 结 语

设计了一种基于FPGA高斯白噪声发生器,分析了该种噪声发生器所用的m序列发生算法,FIR数字滤波算法和DDS算法,可产生带宽为3~66 MHz,步进3 MHz,幅度8位可调的高斯白噪声;采用现场可编程门阵列(FPGA)实现噪声发生器的设计,在Altera公司的QUARTusⅡ软件环境下,实现了基于FPGA的m序列产生模块、FIR数字滤波器模块、DDS模块和合成模块,通过数/模转换器和低通放大,得到了可用于雷达系统和通信信道测试的高斯白噪声信号。实验结果验证了本文设计的有效性。