图6 有效视频的采集流程

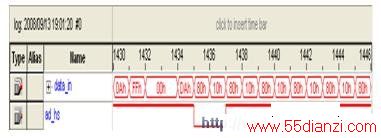

文中按照上述流程设计完成了 图像采集 程序,图7为利用Quartus II自带的逻辑分析仪工具得到的采集图像数据波形图,其中逻辑分析仪的采样时钟为27M的ADC_LLC信号,data_in为图像数据,ad_hs为水平同步信号。

图7 FPGA采集得到的图像数据信号

4.3 视频图像存储模块和DA转换模块

由于FPGA内的RAM资源有限,并为了以后扩展方便系统外加了两片512K*8的SRAM存储器缓存采集的视频数据。当一帧图像采集完成后,FPGA将SRAM中的数据写入DA转换芯片,同时开始下一帧的采集。在本系统中视频编码芯片接收标准的8位CCIR-656数据,输出为CVBS复合视频信号。ADV7177的初始化配置和工作过程与ADV7181类似,这里不再赘述。

5、实验结果

按照以上设计方案,完成了系统的硬件设计和软件调试,图8为系统采集得到的在监视器上显示的一幅视频图像,其中ADV7181采用的是8位CCIR-656输出格式,ADV7177的输出格式为CVBS视频信号。

图8 系统采集的一幅视频图像

6、结论

实验结果表明,本系统工作稳定可靠,可满足于高性能的实时图像处理系统要求。此外,系统采用了FPGA设计方案,集成度高、设计灵活,而且用户可根据自己的需求进行系统重构,方便快捷,具有较高的应用价值。

本文关键字:暂无联系方式DSP/FPGA技术,单片机-工控设备 - DSP/FPGA技术