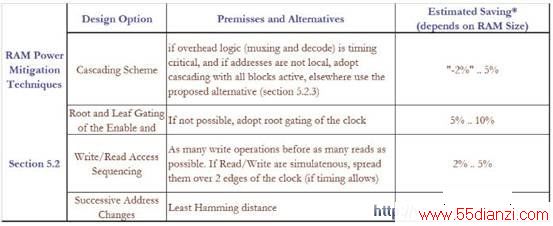

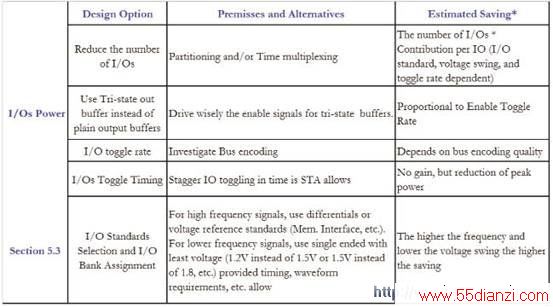

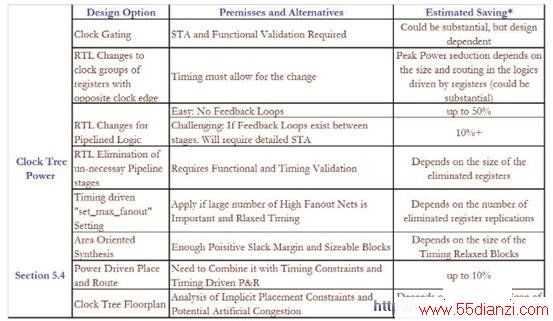

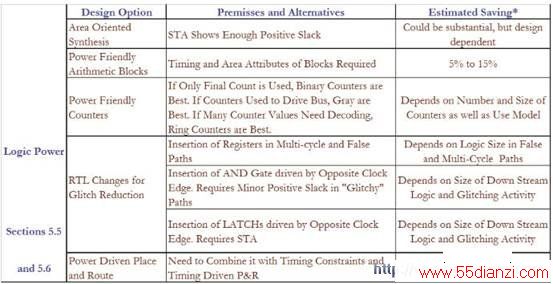

建议设计者要了解最终系统的运行模式,以及每种模式下系统的功耗概况。如果系统处于睡眠模式或者关闭模式的时间较长,需要观察浪涌电流和编程电流的影响,并处理好静态功耗。需要检查设计的动态功耗概况,找出功耗的主要瓶颈,根据概括表(图5~图8)找出最好的解决方法。

图5 RAM 动态功耗概括表

图6 I/O功耗概括表

图7 时钟树功耗概括表

图8 逻辑功耗概括表

在对照概括表之前,只要时序允许,可以修改RTL代码;保证修改以后的功能和时序有效性;也可以尝试调整综合选项以及使用基于功耗优先的策略来进行布局布线。

本文关键字:暂无联系方式DSP/FPGA技术,单片机-工控设备 - DSP/FPGA技术