1 概述

FPGA 仿真 方法:

(1)交互式仿真方法:利用EDA工具的仿真器进行仿真,使用方便,但输入输出不便于记录规档,当输入量较多时不便于观察和比较。

(2) 测试 平台法:为设计模块专门设计的仿真程序,可以实现对被测模块自动输入测试矢量,并通过波形输出文件记录输出,便于将仿真结果记录归档和比较。

2 仿真程序的设计方法

1.仿真的三个阶段:

(1)行为仿真:目的是验证系统的数学模型和行为是否正确,对系统的描述的抽象程度较高。在行为仿真时,VHDL的语法语句都可以执行。

(2)RTL仿真:目的是使被仿真模块符合逻辑综合工具的要求,使其能生成门级逻辑电路。在RTL仿真时,不能使用VHDL中一些不可综合和难以综合的语句和数据类型。该级仿真不考虑惯性延时,但要仿真传输延时。

(3)门级仿真:门级电路的仿真主要是验证系统的工作速度,惯性延时仅仅是仿真的时候有用在综合的时候将被忽略。

2.仿真程序的内容

(1)被测实体的引入。

(2)被测实体仿真信号的输入。

(3)被测实体工作状态的激活。

(4)被测实体信号的输出

(5)被测实体功能仿真的结果比较,并给出辨别信息

(6)被测实体的仿真波形比较处理

3.仿真要注意的地方

(1)仿真信号可以由程序直接产生,也可以用TEXTIO文件产生后读入。

(2)仿真程序中可以简化实体描述,省略有关端口的描述。仿真程序实体描述的简化形式为:

ENTITY 测试平台名 IS

END 测试平台名;

(3)对于功能仿真结果的判断,可以用断言语句(ASSORT)描述

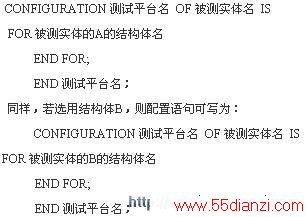

(4)为了比较和分析电子系统的功能,寻求实现指标的最佳结构,往往利用一个测试平台对实体的不同结构进行仿真,一般是应用配置语句为同一被测实体选用多个结构体。

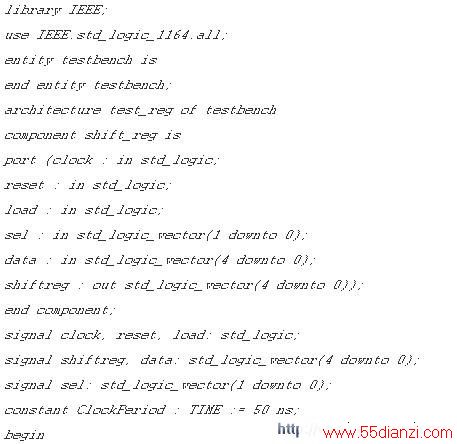

4.VHDL仿真程序结构

测试平台仅仅是用于仿真,因此可以利用所有的行为描述语言进行描述,下表表示了一个测试平台所包含的部分,典型的测试平台将包括测试结果和错误报告结果。

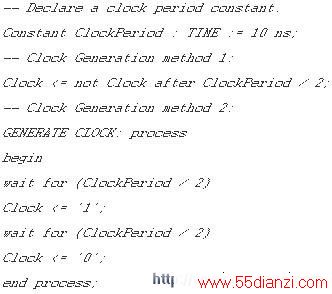

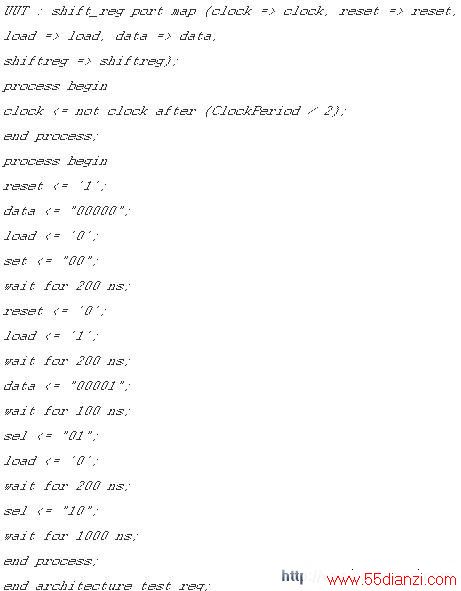

(1)产生时钟信号

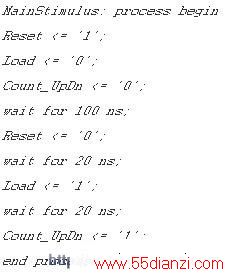

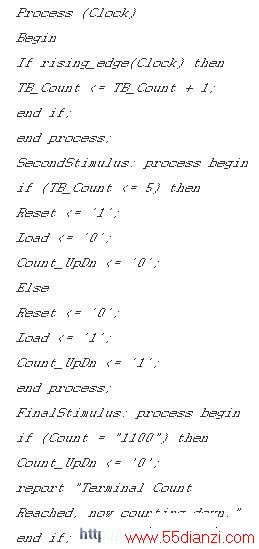

(2)提供仿真信号

提供仿真信号可以有两种方法:绝对时间仿真和相对时间仿真。在绝对时间仿真方法中,仿真时间只是相对于零时刻的仿真时间。在相对时间仿真方法中,仿真的时间首先提供一个初值,在后继的时间设置中相对于该初始时间进行事件动作。

绝对时间仿真:

相对时间仿真:

(3)显示结果

VHDL提供标准的std_textio函数包把输入输出结果显示在终端上。

5.简单的仿真程序

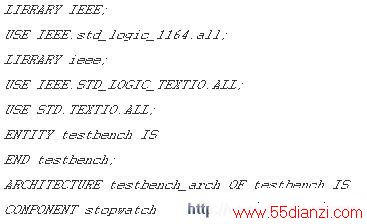

6.3.3 TEXTIO建立测试程序

在由仿真程序直接产生输入信号的方法中,测试矢量是仿真程序的一个部分,如果系统比较复杂,测试矢量的数目非常大,修改测试矢量时就必须修改程序,重新编译和仿真。工作量大。因此,在测试矢量非常大的时候可以用TEXTIO的方法来进行仿真。

TEXTIO仿真方法:测试矢量从仿真程序中分离出来,单独存于一个文件中(即TEXTIO文件),在仿真时,根据定时要求按行读出,并赋予相应的输入信号。这种方法允许采用同一个测试平台,通过不同的测试矢量文件进行不同的仿真。值得注意的是,测试矢量文件的读取,需要利用TEXTIO程序包的功能。在TEXTIO程序包中,包含有对文本文件进行读写的过程和函数。

本文关键字:暂无联系方式DSP/FPGA技术,单片机-工控设备 - DSP/FPGA技术

上一篇:改变设计方法