2.2 系统仿真与验证

在ISE集成环境下,调用ModelSim仿真软件对系统各模块进行功能仿真、综合后仿真以及布局布线后的时序仿真。仿真结果表明,复接器、分接器、同步单元等所有模块的设计均满足设计要求。

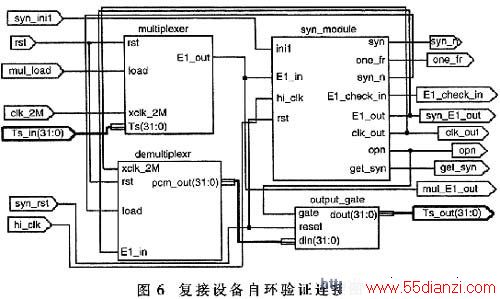

为了进一步确保系统设计的可实用性,将系统各组成模块按照自环工作状态连接起来,对系统各模块进行了联合仿真。复接设备自环验证的原理图如图6所示。

将32路64kbps的支路信号Ts_in(31:0)送到复接器(multiplexer)的支路信号输入端Ts(31:0),复接器的合路信号输出端E1_out与同步单元syn_module(包括位同步和帧同步)的合路信号输入端E1_in相连(自环),合路信号经过位同步信号提取以及帧同步检测后,由同步单元将非失步状态下的合路序列从信号输出端E1_out送出,同步单元还提供位同步信号clk_out,送分接器demultiplex的输入端xclk-2M,同步单元输出的合路序列送入分接器的合路信号输入端E1_in,经过分接器实施分接后,最后从支路输出控制单元output_gate的输出端可以得到各个支路的输出信号Ts_out(31:0)。

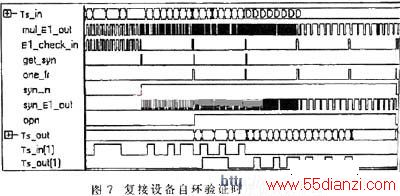

图7为复接设备自环验证的仿真时序图。其中,Ts_in为32个支路送来的64kbps的激励信号;mul_E1_out为经复接器实施复接后的合路信号;E1_check_in为进入帧同步码检测模块的合路序列;get_syn为帧同步码检测的结果;one_fr为同步校核和同步保护所需的帧同步码检测控制信号;syn_n为系统失步信号;syn_E1_out为非失步状态下的合路序列;opn为支路信号输出允许信号;Ts_out为实施分接后各支路的64kbps输出信号;Ts_in(1)为复接器第一支路输入信号;Ts_out(1)为分接器第一支路输出信号。

将输入激励信号Ts_in与系统支路输出信号Ts_out相比较,结果表明,在从同步到下一次失步的时间内,Ts_out与Ts_in信号波形基本一致――Ts_out中会出现一些1~2ns的过渡值,这些过渡值是由于Ts_out总线中32个支路信号到达寄存器输出端的时间不一致而造成的,这是由 FPGA 器件时延不确定性决定的。由Ts_in(1)和Ts_out(1)的波形比较可知,对于每个单一的支路信号,并不存在这种过渡值,分接后的支路信号与复接器支路输入信号一致。因此,Ts_out总线中出现的这种过渡值不会影响系统的性能。

时序仿真结果表明,复接、同步以及分接功能均正常,满足设计要求。在5万门的SPARTAN-3系列FPGA器件xc3s50上实现设计,硬件资源的使用情况如下:319个SlICe,263个Slice flip Flop,562个4 input LUT,70个bonded IOB,2个GCLK。该设计已作为一个模块应用到其它系统中,具有一定的实用价值。同时,由于该设计采用VHDL语言描述,具有可移植性,利用中小容量的FPGA就能实现该系统功能。

本文关键字:暂无联系方式DSP/FPGA技术,单片机-工控设备 - DSP/FPGA技术

上一篇:片上系统设计中的事务级建模方法