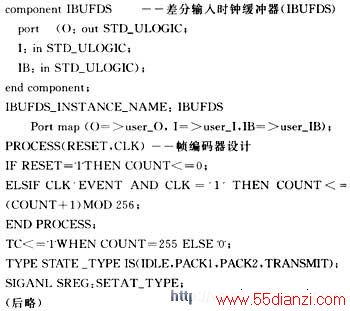

FPGA的部分代码如下:

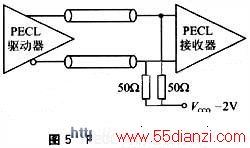

PECL间的连接一般常用直流耦合。在直流耦合情况下,PECL输出设计驱动50Ω负载至(VCC-2V),电路如图5所示。

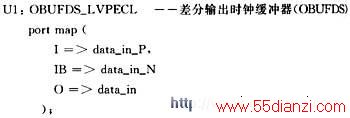

FPGA的部分代码如下:

经实际测试,输入输出指标均符号系统要求,在硬件电路设计中,由于LVDS信号的偏置电压为1.25V,电压摆幅只有350mV,传输速率≥100Mb/s;因此,电路板制作至关重要,要求至少使用四层板。为使干扰信号以共模方式加到差分线对上(不影响数据正确性),要求差分线对间的距离尽可能小。电源方面,FPGA芯片上电时要求有大于500mA的驱动电流,同时,由于多个输出引脚的电位速度变化,要求每对电源和地引脚都要良好旁路。

5 结论

本文给出了基于FPGA高速 数据采集 系统中的输入输出接口的实现,介绍了高速传输系统中RocketIO设计以及LVDS接口、LVPECL接口电路结构及连接方式,并在我们设计的高速数传系统中得到应用。RocketIO传输速度可以达到2.5Gbaud,LVDS总线上的传输速率可以达到120Mb/s,系统性能稳定。