・ MOV TMOD, #01H ;将T0设置为16位定时器

・ SETB ETO ;允许TO中断

・ SETB PTO ;将TO定时溢出中断设置为高级中断

・ MOV TH0,#0;给TO赋初值,定时约130/ms

・ MOV TLO,#0

・ SETB TR0 ;启动T0开始定时

・ SETB EA ;允许CPU中断

另外,TO定时溢出中断服务子程序编程如下:

・ INTO-PRo; MOV A,#02H

・ PUSH ACC

・ PUSH ACC

・ RET1 ;中断返回到0202H单元

当用户应用程序运行正常时,在小于130 ms的时间内,CPU应该及时“喂狗”一一执行清狗指令“MOV THO,#0”和“MOV TLO,#0”。这样,TO就不会产生定时溢出,从而T0定时溢出中断服务子程序不会被执行。但是,当单片机应用系统的CPU受干扰而使程序失控时,CPU就不会及时执行清狗指令,以致于产生TO定时溢出中断,就可以马上将跑飞的程序拉回到正确的轨道。实现及时“喂狗”的具体方法是在用户应用程序中的适当位置插入指令“MOV TH0,#0”和“MOV TLO,#O”。实际上,TO定时溢出中断服务子程序就是一个软件陷阱,一旦执行T0定时溢出中断服务子程序,就是把跑飞的程序强行拉回到0202H程序存储器单元。由前面的分析可知,已经跑飞的程序可以迅速地被纳入正确的轨道。

(4)在未使用的程序存储器地址空间

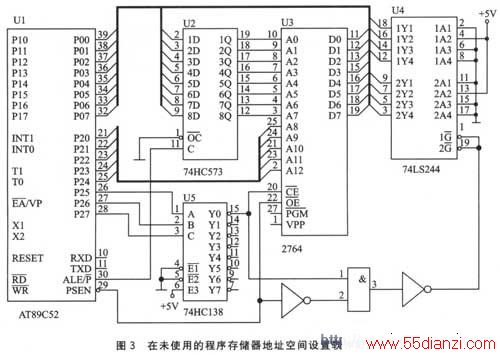

对MCS-51系列单片机而言,程序计数器PC的寻址范围是0000H~FFFFH,共64 KB;然而,在实际的单片机应用系统中,一般没有使用到64 KB的程序存储器,这样就会余下大量的程序存储器地址空间。例如,系统中仅选用了1片2764作为程序存储器,其地址空间为8 KB。那么将有56 KB程序存储器地址空间被闲置。当CPU受到干扰而使程序计数器PC指向这些被闲置的程序存储器地址空间时,CPU取指令得到的指令代码为“0FFH”(这个结论可以根据图3所示电路分析后得出)。该代码是“MOV R7,A”指令的机器码。显而易见,当单片机应用系统的CPU受干扰而使程序失控时,程序计数器PC指针一旦落入这些被闲置的程序存储器地址空间时,CPU执行该指令不仅将错误地修改寄存器R7的内容,而且无法将跑飞的程序纳入正确的轨道。可以使用下面的软件陷阱技术解决这个问题。

如图3所示,EPROM芯片2764的地址空间为0000H~lFFFH,译码器74LSl38的输出Y0为其片选信号,2000H~FFFFH为未使用的程序存储器空间。当程序计数器PC的值落入2000H~FFFFH空间时,一定有Y0为高电乎;当取指令操作时,PSEN为低电平,则74LS244的选通信号有效,所以74LS244被选中。进一步分析图3所示电路可知,当用户应用程序失控而程序计数器PC指向被闲置的程序存储器地址空间2000H~FFFFH时,总线驱动器74LS244被选通,这时CPU通过总线读入的指令机器码为020202H,正好是一条转移指令“LJMP0202H”,这样,使程序计数器PC指向0202H程序存储器单元。由前面的分析可知,已经跑飞的程序可以迅速地被纳入正确的轨道。

(5) 对外部RAM写操作实旆监控保护而设置软件陷阱

在单片机应用系统的外部数据存储器RAM中,一般保存了大量的预置数据和程序运行时产生的中间数据。外部数据存储器RAM的写入是由 “MOVX@ DPTR ,A”指令来完成的。当CPU受干扰程序跑飞而误执行了该指令时,就会改写RAM中内容,导致RAM中的重要数据丢失。为了减小这种RAM中数据丢失的可能性,应在外部RAM写操作之前,对写操作进行条件判断。如果条件满足才执行写入操作;如果条件不满足,则将写入操作屏蔽,并使程序落入陷阱,进入死循环。在程序落人死循环陷阱后,便只能由其他软、硬件 抗干扰 技术(如看门狗技术)使系统退出死循环陷阱,从而使系统恢复正常。具体源程序代码如下(不妨设要写入外部RAM的内容存放在累加器A中,要写入数据的外部RAM单元地址存放在DPTR中):

・ MOV 6EH, #55H

・ MOV 6FH, #OAAH

・ LCALL WRLTE

・ RET

・ WRITE:NOP

・ CINE 6EH,#55H, TRAP

;写入条件是(6EH)=#55H

・ CJNE 6FH,#OAAH,TRAP且(6FH)=#OAAH

・ MOVX @DPTR,A

・ NOP

・ M0V 6EH,#00H

・ M0V 6FH,#OOH

・ RET

・ TRAP, SJMP TRAP ;落入死循环陷阱

4 结 论

与第1种形式的软件陷阱技术比较,第2种形式的软件陷阱技术消除了两个严重的隐患,因此,第2种形式的软件陷阱技术是一种有效实用的单片机应用系统抗干扰技术。本文所介绍的软件陷阱技术已成功地使用在多个实际的单片机应用系统中,保证了系统的可靠运行。

上一篇:嵌入式存储技术在SoC设计的应用