与其他开发小组一样,我们的开发小组也分别由不同的硬件和软件开发人员组成。对于维持开发人员的生产力以保证项目的成功来说,在这两个设计领域之间保留足够的抽象非常关键。我们利用Xilinx Platform Studio中的Create IP Wizard来改进这一任务,为硬件加速模块生成RTL模块和软件驱动文件。这些模块包括访问寄存器所需要的接口逻辑、嵌入式系统中的DMA逻辑和FIFO。一旦利用模块创建了RTL,我们就将其放到嵌入IP目录中,设计人员可根据需求进一步修改。

我们的IP内核开发流程包括一个通用的标准外设模块开发流程,用于基于PLB46MPMC-OPB的回传。这些外设包括单端和多I/O原型(SIMO, MIMO, MISO模型),支持我们为要求苛刻的图像流处理算法灵活创造多线程协处理器流水线。在设计和定制不同分析引擎的过程中,通过近乎任意次序对IP内核进行组合和配置,我们达到了这方面的要求。

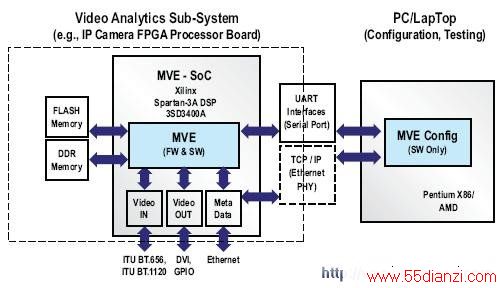

MVE分析引擎由InstantVision嵌入式软件模块以及构成C-MVA分析协处理器的硬件加速器组成。我们在一片Xilinx Spartan -3A-DSP 3400A FPGA中实现了MVE的原型,并创建了 SoC 参考设计。其中包括所有通信和数据流所需要的I/O功能(参考图2了解完整的硬件固件框图)。 这一完整的SoC参考设计使用了91%的逻辑片资源、81%的块RAM和32%的DSP逻辑片,不仅包含MVE分析引擎,还包括所有支持I/O模块。

单就MVE分析引擎来说(不包括MPMC-PLB主干和专用I/O组件),它仅使用了46%的逻辑片、44%的块RAM和23%的DSP逻辑片,因此可以将其移植到成本更低的Spartan3A-DSP 1800A FPGA器件。

在单个时钟周期内,我们设计的CMVA协处理器中所有IP内核可以完成所有相关处理。这一功能与异步FSL接口相结合,系统集成商能够利用来自系统其它部分的不同时钟域来驱动C-MVA协处理器。这样做可以让C-MVA在较低的像素时钟频率中运行,同时利用更高频率的内部系统时钟来驱动主干(backbone),从而在保证系统性能要求的同时大大降低功耗。

定制、封装和系统集成

为验证并进一步开发这一系统,我们创建了一个包括所有软件层在内的安全/监控应用,允许用户在系统的不同层面快速集成我们的产品(参见侧栏)。完整SoC设计在单个参考设计中包括硬件IP内核、固件和软件,请见图5。

图 5. 完整的硬件-固件-软件参考设计

我们可在硬件、固件和软件组件等不同层次进行灵活定制以组成系统集成。服务器级的定制包括FPGA中的可定制SoC设计,而在客户(配置)一级,则可在WIN32 或 .Net API层进行修改。这种架构使我们及客户可快速实现不同配置和测试接口的原型。

用户可以在UART或TCP/IP上实现客户-服务器(C/S)通信,从而提供灵活的配置管理、性能精细调整、状态监控和固件升级。

尽管刚刚完成第二代产品,但我们已经开始考虑第三代产品的要求。根据在这一项目中取得的经验,我们在新一代产品中会着重考虑赛灵思的FPGA器件,特别是赛灵思公司正在致力于利用最先进的工艺技术推出更可靠更先进的新器件和DSP功能。

本文关键字:暂无联系方式DSP/FPGA技术,单片机-工控设备 - DSP/FPGA技术