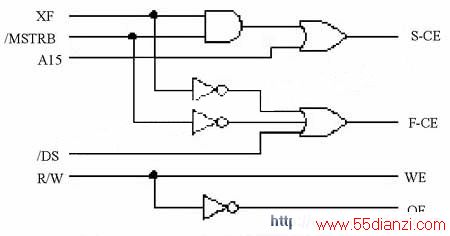

TL16C550C能以16MHz的速度读写数据,读写信号的脉宽很窄,使用一般的串口微处理器误码率较高,而TL16C550C能够很好的与 DSP 匹配。这里VC5402以19200的波特率与PC机通信, 当XIN、XOUT端外接3.072MHz晶振时,波特率因子寄存器的低位的值应为0AH,高位值为00H。C5402与TL16C550C之间的逻辑控制通过CPLD来完成,其内部逻辑如图3所示。

&n bsp; 图3 CPLD中的VC5402与TL16C550C的系统逻辑图

由于RS-232-C电路电平与CMOS电平不同,因此RS232驱动器与CMOS电平连接时必须经过电平转换,本系统采用MAXIM公司的MAX232来完成这一功能。

系统独立工作的程序装载过程

本系统的程序装载分为两部分:C5402(A)自身的并行装载和C5402(B)的HPI装载。

C5402(A)与Flash AT29LV1024和SRAM IS61LV6164之间的逻辑如图4所示。C5402(A)上电复位装载时,由于Bootloader程序在初始化时设置XF为高电平,在系统进入并行引导装载模式后,C5402(A)从数据寻址为0FFFFh单元(A15=1,选中Flash)中读取将要载入的程序存储区首地址和并行装载数据流。此时,C5402可以将 Flash地址08000h-0FFFFh单元中的数据读到C5402对应于0000h-7FFFh寻址区的片内DARAM和片外SRAM中。Bootloader程序结束后用户程序的第一条语句为RSBX XF,置XF引脚为低电平, Flash始终不选通。这样,SRAM的高32K区域(08000h-0FFFFh)被释放出来,可以作为C5402(A)运行时的数据区或程序区使用。C5402(A)装载进来的程序数据主要分三部分:给C5402(B)的装载程序,自身的运行程序及C5402(B)的运行程序。

图4 VC5402与存储器的逻辑图

在C5402(A)进行并行装载的过程中,C5402(B)在判断是哪种装载模式。因为C5402(B)的HINT和INT2连在一起,在DSP上电初始化时将07FH单元清0,同时HINT置0,这样导致了INT2的IFR的相应标志位有效,C5402(B)查询到INT2的标志位有效后,判断是HPI装载模式。C5402(A)在进行完并行装载后,首先运行装载程序,将C5402(B)运行程序数据传送C5402(B)中,最后将C5402(B)的程序入口地址写到07FH单元,表明HPI装载结束。

系统软件设计

系统的软件设计主要包括,多通道缓冲串口的初始化,串口中断服务程序,并行装载程序设计,TL16C550C的初始化及HPI设计等。

程序设计应注意的问题

(1)McBSP工作在数据接收中断方式,因此全局中断和串口中断的相应位应该合理设置。同时,在设置中断向量表时,使中断向量表的位置与处理器模式状态寄存器PMST中的中断向量指针IPTR相对应,使IPTR的9位地址指向128字的中断向量所在的程序页,同时,中断向量表要严格按照C5402规定的格式编写,否则不能正确地产生需要的中断结果。

www.55dianzi.com

(2)要实现 DSP 数据采集系统的脱机独立运行,程序装载十分关键。C5402(A)进行并行装载,要求AT29LV1024中的程序数据流严格按照并行装载的格式,依次给C5402(B)装载程序、C5402(A)自身执行程序,C5402(B)的程序装载到片内DRAM和片外SRAM中。

(3)注意到系统设计中,C5402(B)的HPI口既用来进行程序装载,又作为两片DSP通信接口,为了避免混乱,在C5402(B)的程序中应将IFR中INT2的相应位清零,最好在IMR中屏蔽INT2。

(4)为了实现两路A/D和C5402之间的时序匹配,避免数据冲突,需要注意C5402采样率发生寄存器SRGR1中CLKGDV位的设置,使C5402工作时钟周期大于两个串口中断的响应时间。

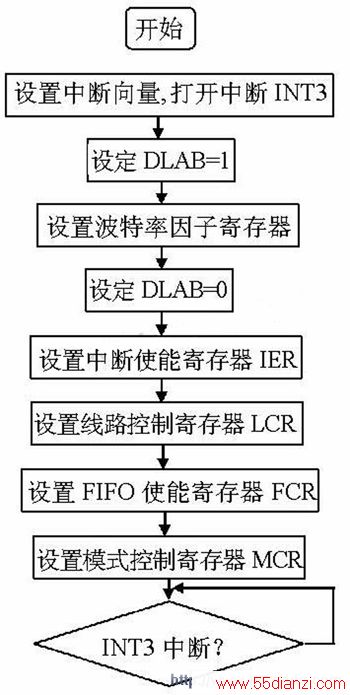

TL16C550C的软件流 程

TL16C550C 初始化程序主要完成波特率及其它工作寄存器的设置。这里设置TL16C550C工作模式为8位数据位,2位停止位,奇校验状态。TL16C550C的软件设置流程如图5所示。

图5 TL16C55C工作的软件流程(略)

串口接收的部分初始化程序

下面根据多通道缓冲串口的特性和两路串行A/D工作的要求,主要介绍一下串口接收的软件设计和串口部分关键设置。

;=====初始化串口0========

stm #0, SPSA0

stm #0000h, SPSD0 ; #0000H SPCR10

stm #1, SPSA0

stm #0000h, SPSD0 ; #0000H SPCR20

stm #2, SPSA0

stm #0040h, SPSD0 ; #0040H RCRC10 每字16位

stm #3, SPSA0

stm #0040h, SPSD0 ; #0040H RCR20 每帧一段,每段一字

stm #6, SPSA0

stm #000fh,SPSD0 ; #0009H SRGR1 时钟周期 CLKG="6".4MHz

stm #7, SPSA0

stm #300fh, SPSD0 ; #3010H SRGR20 帧周期为16个CLKG

stm #0eh,SPSA0

stm #0a04h, SPSD0 ; #0A04H PCR0 FSX, CLKX输出,FSR,

CLKR输入

;=====初始化串口1======

串口1的初始化程序参见串口0

www.55dianzi.com

;=====启动接收========

stm #0,SPSA0

stm #0001h, SPSD0 ;启动串口0接收

stm #1,SPSA0

stm #00c0h, SPSD0 ;内部产生时钟产生FSG

stm #0,SPSA1

stm #0001h, SPSD1 ;启动串口1接收

stm #1,SPSA1

& nbsp; stm #00c0h, SPSD1 ;内部产生时钟产生FSG

;==串口0接收中断子程序===

.sect "brint0"

host_brint0:

rsbx intm ;关中断

ldm drr0,A

stl A,*ar4+ ; 接收

:::

其它处理程序

rete

结束语

本文利用两片 DSP ,根据TM320C5402多通道缓冲串口的特点,提出了由四个阵列天线传感器阵元组成的DOA估计硬件设计方案,并给出了系统独立工作的硬件原理图和软件设计的部分关键程序。并行装载模式和HPI装载模式同时使用,有效利用了系统资源,减小成本,同时TL16C550C的使用实现了DSP与PC机的高速串行通信。

本文关键字:无线 DSP/FPGA技术,单片机-工控设备 - DSP/FPGA技术