此时一片FPGA内集成了编码器和解码器,与MPU相连的数据通信接口仍为8位数据线,由MPU发W/R写读信号来控制编解码,因此同一时间只能单向传送数据,编解码不能同时进行。准确地说,为半双工通信。(要改为全双工,须将MPU的数据线接口翻倍,非常占资源。)

双工电路原理如图6所示。

双工编、解码器的内部电路如图7所示。(编码器,解码器与单工的相同。)

实际上,我们对编码器和解码器的输出分别加了一个传输门(transfer_X器件)。该传输门由W/R信号控制,一旦传输门关闭,则将传输门的输出置于高阻态("Z"),因此,编解码器的输入输出不会相互干扰,从而能在同一数据线上进行半双工传输。

MPU向FPGA写信息,FPGA编码输出。W/R=0,信息为11001010。

MPU读FPGA的信息,FPGA收帧结构并解码。W/R=1,解码得11001010。

4 总结

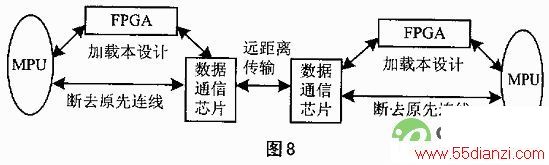

①我们的设计目的主要在于增加数据的容错能力。FPGA设备加载于MPU的数据接口与数据通信芯片接口之间,数据仍按原系统的发送方式远距离传输,如图8所示。因此原有的通信设备不必作改动,就能很方便地加载我们的设计。同时,因为编码采用的分组码的位数可以根据实际应用场合再做简单调整,因而能够提供更大的噪声冗余。

②FPGA内部提供统一的编解码波特率,最高由FPGA时钟频率决定,仿真图中采用100ns(10MHz)。MPU收发信息的波特率最高为编码波特率的1/8,因为1字节的数据信息要转换为8字节帧结构。也就是说,我们是以降低通信的最高速率为代价来换取数据的高精度的。因此,我们的设计主要应用于不要求过高速率的通信场合。

本文关键字:暂无联系方式DSP/FPGA技术,单片机-工控设备 - DSP/FPGA技术

上一篇:用CPLD实现单片机读写模块