随着高速A/D转换技术和DSP技术的发展,中频数字处理技术亦得到发展。中频数字处理技术是提高现代通信接收机性能的重要技术之一。作为中频数字处理的核心器件,早期的A/D转换器由于速度和精度的限制,难以满足中频数字接收机高速数字化的要求。本文将以基于软件无线电技术的差分跳频电台中频数字接收机为例,给出一种基于新型ADC器件-AD6644的中频数字处理模块的设计方案。

1系统总体结构设计

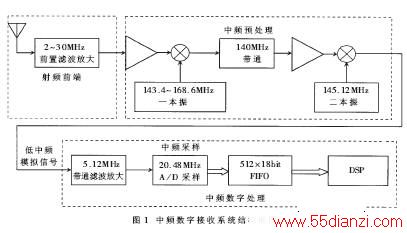

本方案的中频数字接收系统结构如图1所示。因差分跳频系统是一种异步跳频系统,省去了同步电路,结构得以简化。该系统主要由射频前端、中频预处理和中频数字处理三部分组成。系统主要功能为:工作在短波频段(2~30MHz),对跳频速率为5000跳/s、带宽为2.56MHz的信号进行不低于12bit的采样,以合适的数据率送入DSP,然后由DSP完成各种算法处理。

射频信号先经过2~30MHz的前置滤波放大电路放大。为了有效抑制组合频率干扰和副波道干扰,本系统的中频预处理部分采用高中频方案

本文关键字:暂无联系方式DSP/FPGA技术,单片机-工控设备 - DSP/FPGA技术