本应用指南说明了利用 Virtex-5 器件实现 4 字突发四倍数据速率 (Quad Data Rate, QDR II)SRAM 接口及其时序的详细信息。此可综合的参考设计利用 Virtex-5 系列独有的 I/O 和时钟控制功能,实现了 300 MHz (600 Mb/s) 的性能水平,使每个 36 位存储器接口的总流量达到 43.2Gb/s。

此设计在最大限度降低资源使用量的同时还大幅简化了在 FPGA 内采集读数据的任务。此方案提供了一个简单的用户接口,可通过利用一个或多个 QDR II 接口简便地集成到一个完整的FPGA 设计中。

简介

QDR SRAM 器件为满足更高的带宽存储要求而开发,以网络和电信应用为目标。基本 QDR 架构具有独立的读、写数据通路,便于同时操作。每个时钟周期内,两个通路均使用双倍数据速率 (DDR) 传输发送两个字,一个在时钟上升沿发送,一个在时钟下降沿发送。结果,在每个时钟周期内会传输四个总线宽度的数据(两个读和两个写),这就是四倍数据速率的由来。

QDR I 和 QDR II 的规范由 QDR 联盟(Cypress、IDT、NEC、Samsung 和 Renesas)共同定义和开发。有关 QDR 规范、QDR 联盟和 QDR 存储器产品的其他信息,请参考第 16 页上的“参考”。

QDR 存储器器件以 2 字突发和 4 字突发架构提供。针对每个读或写请求,2 字突发器件传输两个字。DDR 地址总线用于在前半个时钟周期允许读请求,在后半个时钟周期允许写请求。与之相反,4 字突发器件针对每个读或写请求传输四个字,这样便只需要一个单倍数据速率 (SDR)地址总线,就能最大程度地利用数据带宽。读、写操作请求必须在交替的时钟周期(即不重叠的时钟周期)内进行,以分享地址总线。

本应用指南所讨论的参考设计针对的是 4 字突发 QDR II SRAM 器件。QDR II 架构的独特性能之一是源同步回送时钟 (CQ) 输出,它与器件输入时钟 (K) 频率相同,与通过读通路输出 (Q) 传输的数据边沿对齐。CQ 时钟输出使用 QDR II 存储器器件内的延迟锁定环 (DLL) 电路被重新安排,使其与 Q 数据输出对齐。对于在远端器件上进行的读数据采集操作,此种时钟传输(亦称源同步)接口方法允许较大的时序余量。

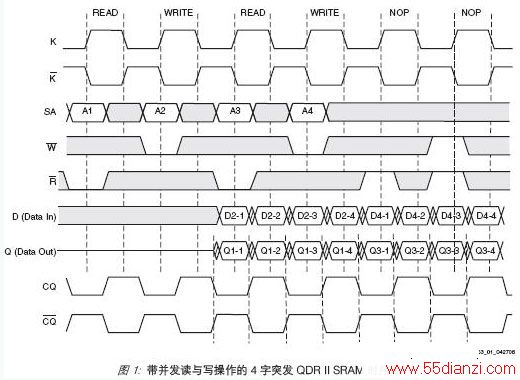

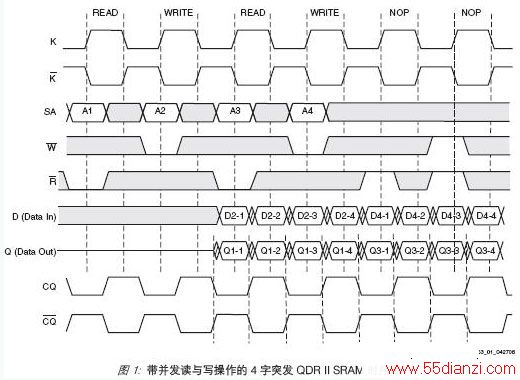

第 2 页图1 的时序图表示 4 字突发 QDR II 存储器接口上的并发读/ 写操作。QDR II 存储器的所有输入与输入时钟(K 和 K)同步,传输给存储器时,数据中心通常与输入时钟 K 及 K 边沿对齐。

注: 低有效的读控制 (R) 和写控制 (W) 引脚在时钟周期内交替出现,以实现单独 SDR 地址总线 (SA) 的共享。

写总线数据输入 (D) 值在 DDR 模式下被发送到存储器,开始于写控制引脚激活后的下一个K时钟上升沿。读总线数据输出 (Q) 值在 DDR 模式下从存储器中发送,并与 CQ 和 CQ 源同步回送时钟输出边沿对齐。在 CQ 时钟输出的上升沿(紧随 K 输入时钟的下一个上升沿之后),读总线中的第一个字开始发送。

在从数据输入 (D) 字中选择要写入存储器的特定字节时,QDR II 存储器还可使用低有效的字节写 (BW) 使能引脚。为清晰起见,图1 中省略了这些信号。

图1 的时序图表示 2 字突发 QDR II 存储器接口上的并发读/ 写操作。在时钟的前半个周期,DDR 地址总线允许读地址被传输给存储器;在时钟的后半个周期,DDR 地址总线允许写地址出现于其中。因此,低有效的读控制 (/R) 和写控制 (/W) 引脚可在同一时钟周期内设定。

两个写总线数据输入 (D) 值在 DDR 模式下被发送到存储器,开始于写地址有效前的那个 K 时钟上升沿。读总线数据输出 (Q) 值在 DDR 模式下从存储器中发送,并与 CQ 和 /CQ 源同步回送时钟输出边沿对齐。在 /CQ 时钟输出的上升沿(紧随 /K 输入时钟的下一个上升沿之后),读总线中的第一个字开始发送。

设计概述

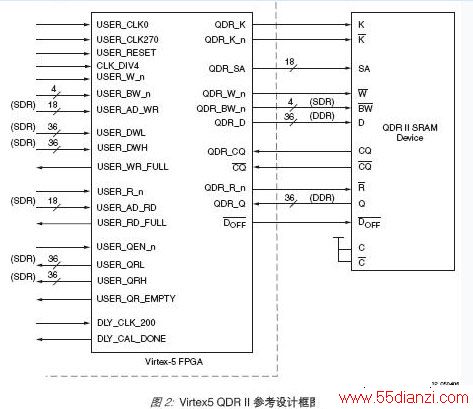

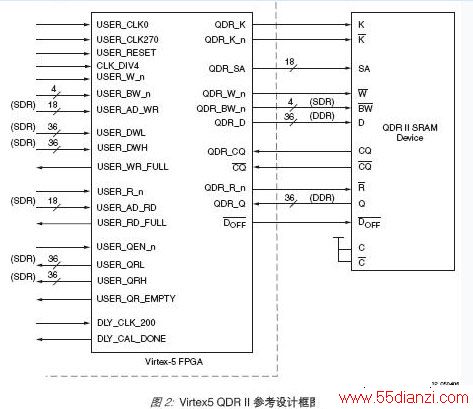

图2 为 Virtex-5 QDR II 参考设计的高层次框图,表明了 QDR II 存储器器件的外部连接以及用于发送读/ 写命令的 FPGA 内部资源接口。

在图2 中,QDR II 器件的 C 和 C 引脚均被设定为 High。

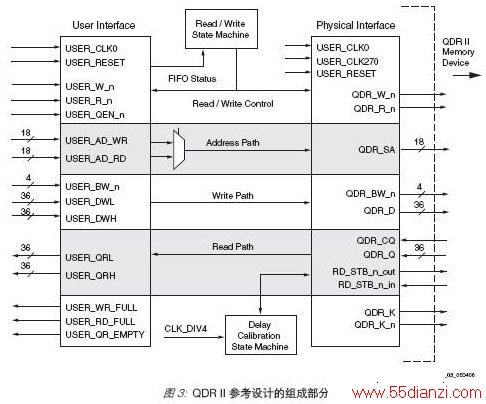

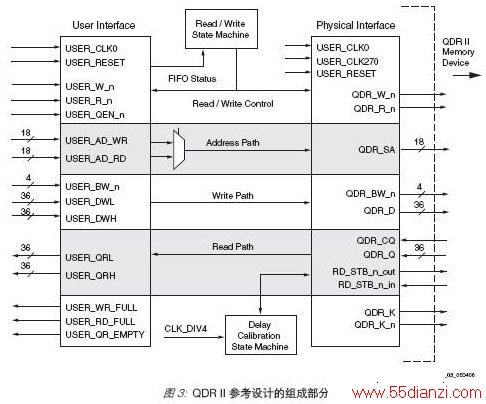

如第 4 页图3 所示,Virtex-5 QDR II 参考设计由以下四个主要部分组成:

用户接口

物理接口

读/ 写状态机

延迟校准状态机

此用户接口使用完全基于 SDR 信号的简单协议创建读/ 写请求。此模块主要由 FIFO16 基元构成,用于在读/ 写操作执行前后存储相应的地址和数据值。有关用户接口时序协议的详情,请参阅第 5 页“用户接口”。

读/ 写状态机主要负责监控用户接口模块内 FIFO 的状态,调整用户接口和物理接口间的数据流,并向外部存储器器件发送实际读/ 写命令。此状态机确保读/ 写操作按照 QDR II 存储器规范的要求,以并发方式在最短延迟内完成。

物理接口负责生成正确的时序关系和 DDR 信号,以便以符合其命令协议和时序要求的方式与外部存储器器件通信。

延迟校准状态机是物理层中一个不可分割的组成部分,大大简化了在 FPGA 内采集读数据的任务,同时又可实现最佳性能。Virtex-5 器件的每个输入引脚都包含一个可动态调整的可编程延迟元件 (IDELAY),用于控制 5 ns 窗口中输入通路上的延迟时间。延迟校准状态机利用此独特功能调整从存储器器件返回的读数据的时序,因此它无需任何复杂的数据采集技术即可直接与全局 FPGA 系统时钟 (USER_CLK0) 实现同步。

第 5 页表1 总结了 Virtex-5 QDR II 参考设计的规范,包括性能目标和器件应用细节。

实现详情

实现QDR II 参考设计的目的是利用 Virtex-5 系列的独特功能。I/O、时钟控制和存储元件技术方面的发展使此设计的高性能和全承包操作得以实现。以下部分对此设计的实现给出进一步的详细说明。

本文关键字:接口 ARM单片机,单片机-工控设备 - ARM单片机