一种可在电路输入级使用的简单的ESD瞬变抑制技术,就是将一个磁珠串在输入引线上,并在输入引线和地之间接一只容量很小的电容器。图2示出了磁珠的等效电路。输入端的LC电路起滤波器的作用,将ESD瞬变的能量分流入地。当使用瞬变抑制二极管保护任何输入端或输出端时,要使瞬变抑制器尽量靠近这些端子。很长的导线和电路板印制线都有寄生电感,当ESD瞬变脉冲进入电路时,寄生电感就会产生电压过冲与振铃问题。

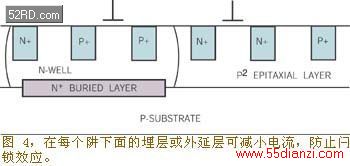

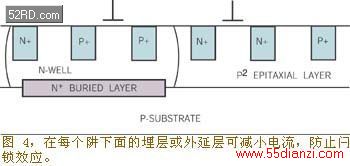

你可使用CMOS布局技术来防止闩锁效应,因为CMOS布局技术可监控ESD瞬变会进入器件的各部位:器件的电源引脚、输入引脚和输出引脚。你应降低晶体管(PNP和NPN)的增益,并提高闩锁效应的阈值,方法是加大器件结构中P沟道Tub与P沟道漏极之间的间隔。在电源和p-tub上连接p+和n+保护环也可以降低晶体管增益,提高闩锁效应的阈值(图3)。防止闩锁效应的其他工艺技术有:提高阱深度以减少寄生晶体管的增益;采用绝缘衬底(如蓝宝石硅)以降低tub和衬底中的电流,;在每个阱下面采用埋层或外延层(图4)。

你也可以用良好的电路设计技术来减少ESD危害和与ESD有关的电子器件失效。元器件选用得当和关键部位使用电路级技术(保护网络)均可减少ESD的种种影响。良好的接地与电路板布线技术;在装配、生产和测试时小心取放对ESD敏感的器件;在包装和运输器件和组装电路板时采用适当的防静电包装材料,这些措施都可减少失效。电路屏蔽得当也可以减少ESD的影响。

电路板布局会影响ESD

电路板布局会影响ESD

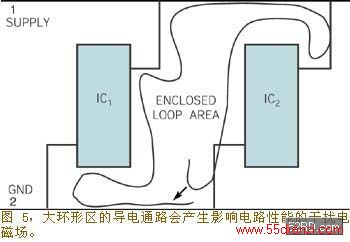

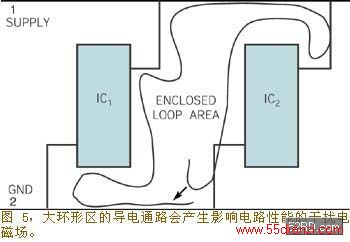

你如果使用布局和布线都很好的电路板,就可以显著减少ESD问题的发生率(见附文《实现ESD故障最小化的电路设计原则》)。每一电路都因为有不同类型的元器件和电流而存在有静电通量线和磁通量线。如果电路板布线围住很大的环形区,则导电通路就会围住较大的磁通量,由于环路起天线的作用,较大的磁通量又会在环路中感应产生电流。这种环路电流会产生影响电路中元器件的干扰电磁场。减小环路区的方法是使电源线和地线尽量靠近在一起。图5示出了典型的电源线和地线形成的环路区。

要在电路板设计中采用低阻抗地线,以便任何ESD电流都能很容易地流入地,而不是经过电子器件的其他低阻通路流入地。一个接地区域,最好是一个接地层,均可降低ESD的影响,因此,你应将电路板上未用区域都变成接地层。使信号线靠近地线也可减小环路面积,并可将大环路引起的ESD问题减至最少。具有独立接地层的多层电路板则更为可取。

在电路板布局时,敏感电子元件要远离潜在的ESD源,如变压器、线圈和连接器。这些潜在的ESD源会积累电荷或产生杂散的电磁场,从而导致元件损坏。对线圈、变压器和类似元件进行屏蔽,以抑制这些元件辐射的电磁场,这是明智之举。要在很长的信号线之间布放一根地线,以减小环路面积。你把敏感电子元器件放在远离电路板边缘的地方,就可避免ESD偶然损坏这些元器件;因为这样做可避免人体接触和可能由ESD引起的损坏。

本文关键字:暂无联系方式电工文摘,电工技术 - 电工文摘