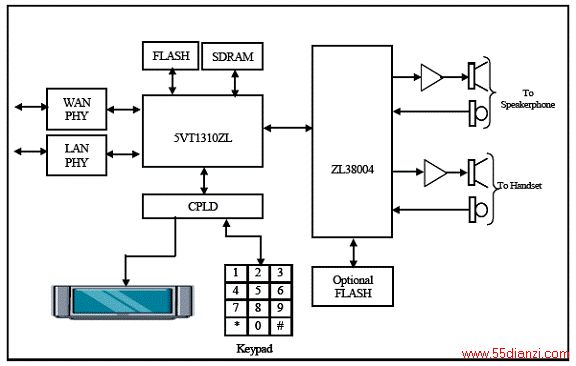

Zarlink公司的 ZLAN-223 IP电话参考设计采用Zarlink公司的 ZL38004语音处理器和 5VT1312 IP处理器,以及以太网 PHY RTL8201。本文介绍了这些器件的主要特性和方框图。此外,还介绍廖参考设计的方框图和详细而完整的电路图。

ZLAN-223:IP Speakerphone Reference Design

This reference design application note outlines a system solution for an IP speakerphone using the Zarlink ZL38004 voice processor and the 5VT1312 IP

processor. The reference design identifies third-party devices required to complete the system. This is a preliminary design and should be considered as a proof-of concept-only at this point. It has been presented to illustrate a theory of operation and to estimate circuit complexity. This reference design will cover the system design from analog microphone/speaker MII including the digital-to-analog and analog-to-digital conversion voice processing and packet processing. The proposal does not include the LCD interface although a CPLD is incorporated into the design to provide a simple interface to a parallel simple LCD module.

图1。IP电话方框图

1.硬件描述:

The IP speakerphone design is based around two main devices: the ZL38004 voice processor and the 5VT1312 IP processor. The ZL38004 performs the audio processing (acoustic echo cancellation, noise reduction and tone generation) provided through the ZLS38502 firmware. Other firmware currently in development will provide addition features, such as voice prompting (with the ZLS38503) and messaging and voice recognition (with the ZLS38504). The 5VT1312 provides all the packet processing Ethernet bridging and call control processing. The 5VT1312 also provides voice compression (G.711/G.G.723/G.726/G.729/iLBC).

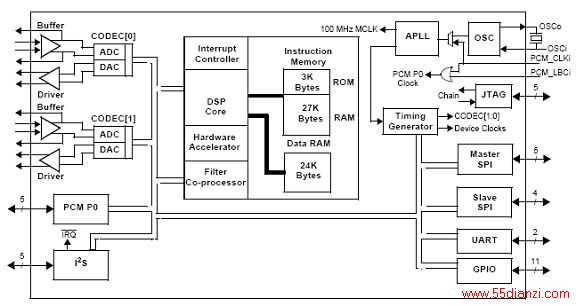

(1)ZL38004语音处理器

ZL38004 Enhanced Voice Processor with Dual Wideband Codecs

The ZL38004 has the following features:

100 MHz (200 MIPs) Zarlink voice processor with hardware accelerator

Dual ADCs with input buffer gain selection and programmable sample rate of either 8 or 16 kHz

Dual DACs with output sampling of 8, 16, 44.1 and 48 kHz and internal output driver

Inter-IC Sound (I2S)

PCM port supports TDM (ST BUS, GCI or McBSP framing) or SSI modes at bit rates of 128, 256, 512, 1024,2048, 4096, 8192 or 16384 Kb/sec

Separate slave (microcontroller) and master (Flash) SPI ports, maximum clock rate = 25 MHz

11 General Purpose Input/Output (GPIO) pins

General purpose UART port

Bootloadable for future Zarlink software upgrades

External oscillator or crystal/ceramic resonator

The DSP Core can process up to four 8-bit audio channels, two 16-bit audio channels or two 8-bit and one 16-bit audio channel. These audio channels may originate and terminate with the CODECs, or be communicated to I2S port.

图2。 ZL38004方框图

(2)5VT1312 IP 处理器

The 5VT1312 in an integrated system-on-chip utilizing the ARM926EJS processor core (operating a 300 MHz) and

AMBA based peripherals. The 5VT1312 chip adopts the ARM AMBA platform architecture and can lower overall

system costs, reduce development cycle time and accelerate product introduction. The following outlines the

5VT1312 features:

300 MHz ARM926EJS with SoftDSP extension

Can process up to 2 voice channels

2 x 10/100 MAC

SPI/UART/GPIOs/Timers/DMA

Soft Codec Support, G.711/G.723.1/G.729/G.729AB/ILBC

FAX Relay, T.38

Tone Generator and Tone Detection

DTMF Relay

NAT Transversal (STUN), UPnP, DHCP Client/Server

Signalling Protocol SIP 2.0 (RFC2543/RFC3261)

SIP Supplementary Service such as Caller ID, Call Waiting, transfer, etc.

QOS - DiffServ

Web Configuration

1.27 V Core, 3.3 V I/O

208 pin PQFP

The 5VT1312 is a derivative and subset of the more extensive 5VT1310. The 5VT1310 can support not only the 5VT1312 features listed above, but also PCI and two additional voice channels. However, for most IP Phone applications, the 5VT1312 should be adequate. Using the integrated PCM ports, 10/100 Ethernet MACs and the available embedded networking and call handling software, a VoIP system can easily be implemented for quick time-to-market requirements.

图3。5VT1310 方框图(没有PCI 接口)

(3)以太网 PHY RTL8201

The RTL8201 is a single-port Voice-over with Media Independent Interface (MII) that implements all 10/100M Ethernet Physical-layer functions including the Physical Coding Sub layer (PCS), Physical Medium Attachment (PMA), Twisted Pair Physical Medium Dependent Sub layer (TP-PMD), 10Base-Tx Encoder/Decoder and Twisted Pair Media Access Unit (TPMAU). It is fabricated with an advanced CMOS process to meet low voltage and low power requirement.

The Realteks RTL8201 provides the following features:

Support MII interface

Support 10/100Mbps operation

Support half/full duplex operation

IEEE 802.3/802.3u compliant

• Support IEEE 802.3u clause 28 auto negotiation

• Support power-down mode

• Support Link Down Power Saving mode operation

• Support repeater mode

• Speed/duplex/auto negotiation adjustable

• Low operation power consumption

• Adaptive Equalization

• 25 Mhz crystal/oscillator as clock source

• Many LEDs support to indicate network status

• Support 7-wire Serial Network Interface (SNI) interface

• Flow control ability support to co-work with MAC (by MDC/MDIO)

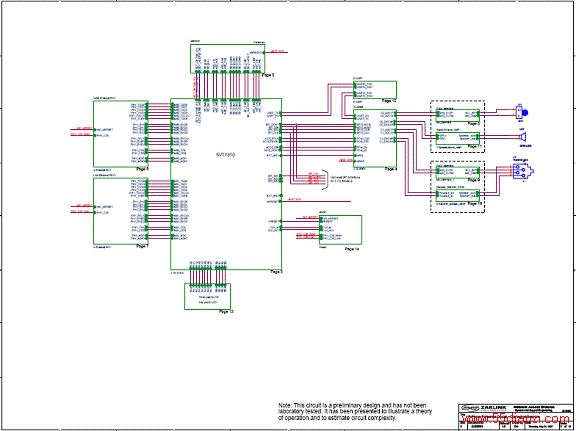

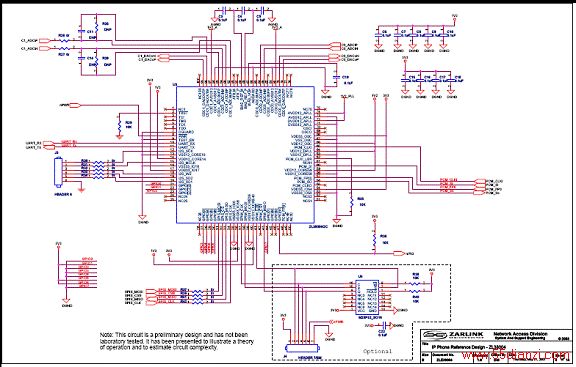

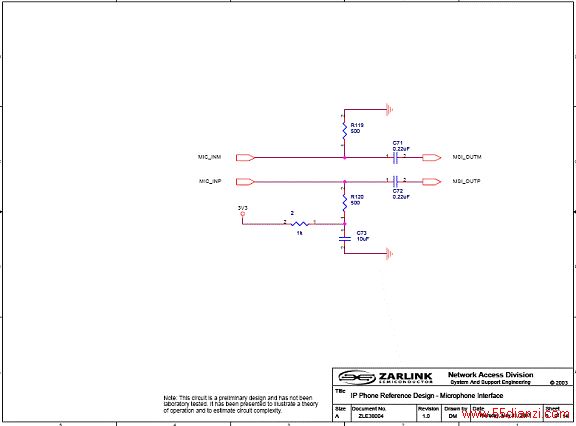

图4。ZLAN-223 IP电话参考设计电路图(1)

图5。ZLAN-223 IP电话参考设计电路图(2)

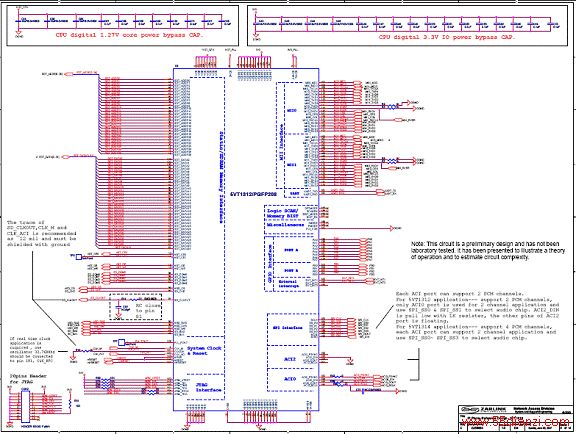

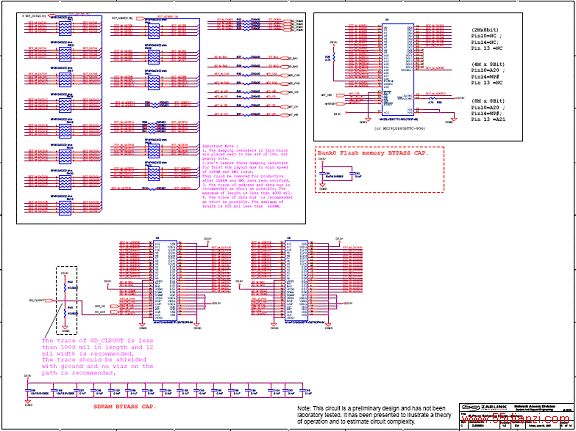

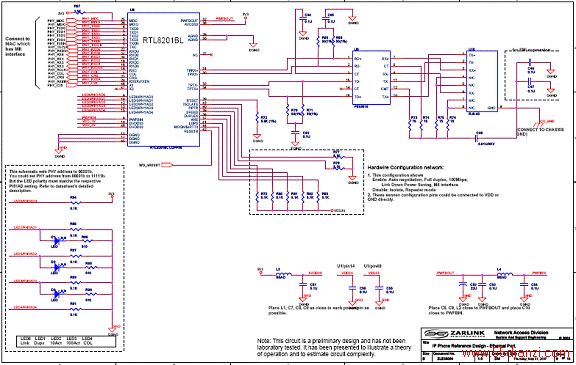

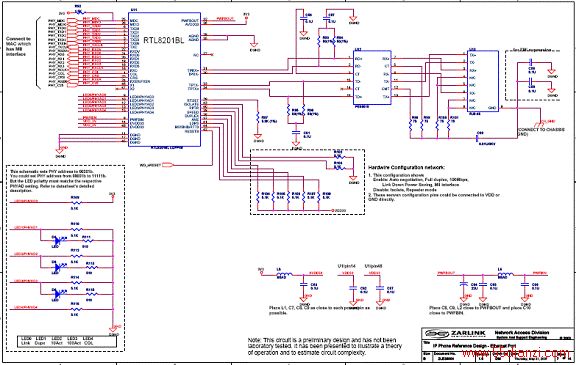

图6。ZLAN-223 IP电话参考设计电路图(3)

图7。ZLAN-223 IP电话参考设计电路图(4)

图8。ZLAN-223 IP电话参考设计电路图(5)

图9。ZLAN-223 IP电话参考设计电路图(6)

本文关键字:电话 电工文摘,电工技术 - 电工文摘