DVB-T解调器的数据传输和前FFT同步系统的

点击数:7625 次 录入时间:03-04 11:54:41 整理:http://www.55dianzi.com 电工文摘

摘要:介绍了DVB-T解调器的整体结构,并设计了一种多模块间进行数据传输的机制,同时还设计了前FFT同步系统,其中包括了基带变换、粗符号同步和分数频率同步。

关键词:DVB-T 同步 多路交叉开关

图1

1 系统整体结构

2 数据传输

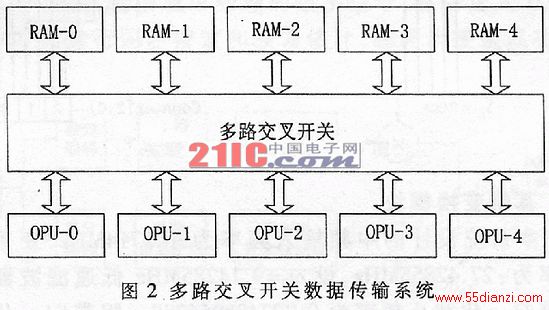

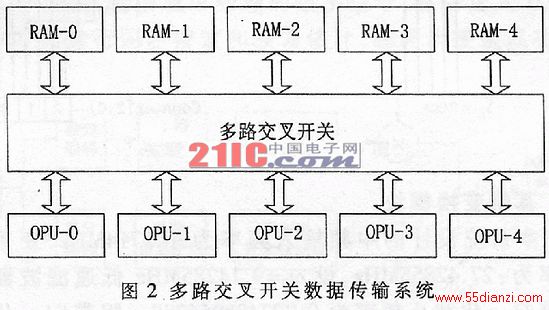

可以看出1bit地址信号的交叉开关需要5个四输入与门和1个五输入或门,总线按照32bit数据(双向)和12bit地址计算,则需要380个四输入与门和76个五输入或门,而且没有一路信号只经过两经门延迟。因此从实现规模和信号延迟上看,这个多路交叉开关都是容易实现的。这个模块在Altera Stratisx1S25 FPGA上验证,其存取速度可以达到100MHz以上。

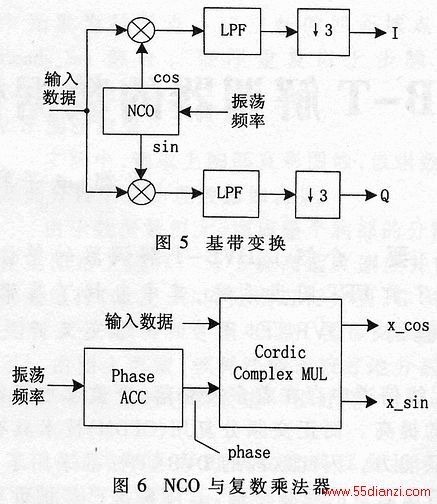

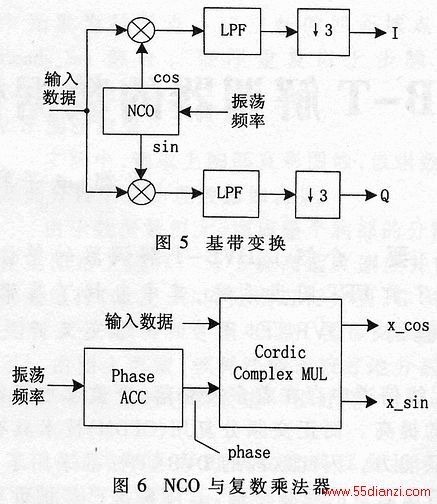

复数乘法器采用Cordic算法实现,相位累加器根据输入的振荡频率调整相位累加的步长,其输出为本地载波的相位。Cordic乘法器的一个乘数为采样数据,另一个乘数就是本地载波的相位,其两个输出分别为输入数据与cos和sin相乘的结果。乘法器的输出进入上面所描述的74阶FIR低通,然后直接进行3倍抽取从而获得速率为9.14MS/s的数据基带信号。

图7

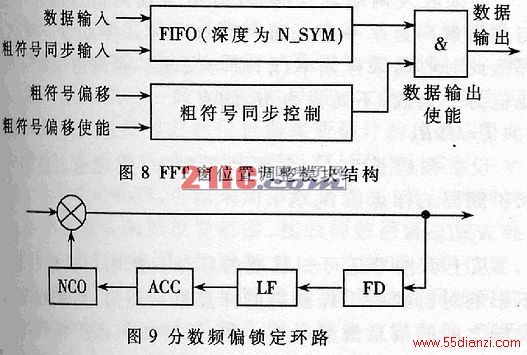

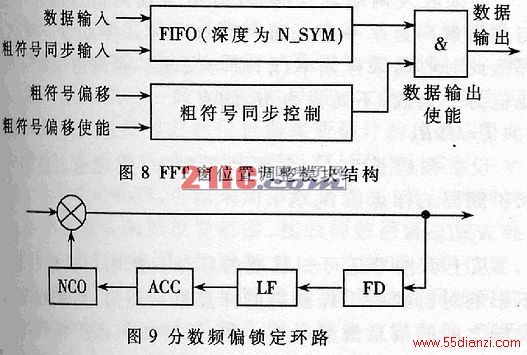

2.2.1 粗符号同步估计

2.2.2 FFT窗位置调整

ACC为累加器。NCO即图5中所描述的数据振荡器。

本文关键字:解调器 电工文摘,电工技术 - 电工文摘