引言

最近几年,低压差分信号(LVDS)[1]的高速数据互连已广泛应用于消费电子产品、高速计算机外设、通信/网络以及无线基站等各个领域。LVDS在性能、功耗、噪声、EMI以及成本等方面具有显著优势。采用正确的设置,LVDS信号可以通过一对儿双绞线电缆提供100Mbps至800Mbps的数据速率,传输距离为10m至15m,在PCB引线上的传输距离> 1m。100负载的功耗仅为1.2mW,与频率无关。

本应用笔记主要讨论LVDS失效保护电路,这对于LVDS正确工作非常重要。将检验三种失效保护电路,并分析它们的特性进而为提供应用指导。

LVDS的基本特性和优点

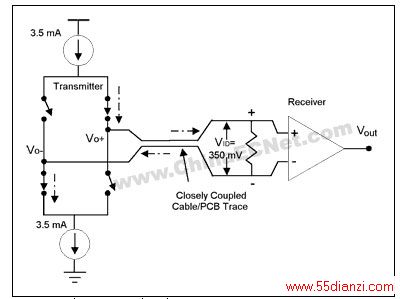

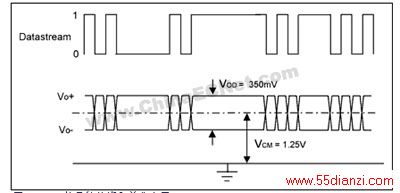

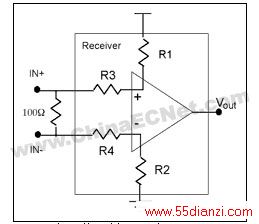

首先简单回顾一下LVDS信号的基本特性和电路配置。图1所示为简单的LVDS发送、接收基本电路,接收器是一个绝对转换门限约为50mV的比较器。传输媒介,无论是电缆还是PCB引线,都设计成100差分阻抗。图2 所示为媒介信号的共模和差分电平。在图1和图2中,VID是LVDS接收器的输入差分电压,VOD是LVDS发送器的差分输出电压,VCM是共模电压。

图1. LVDS的Tx、Rx基本电路图

图2. LVDS信号的共模和差分电压

电流源恒定驱动两条紧密耦合的电缆线或PCB引线,媒介中的共模电流、电压不随时间改变,差分信号随时间变化。通常,数据传输速率主要受负载寄生电容、电感的限制。对于图1所示LVDS电路,驱动器(发送器)的共模阻抗大部分来自负载电容。另一方面,寄生电感主要来自芯片或负载引线,而不是匹配传输线。此外,寄生电感值相对较小,因此对信号完整性的影响可忽略不计。由于负载共模电压不变,负载寄生电容的影响可以忽略。因此,LVDS信号与CMOS或TTL信号相比能够提供更高的数据传输速率。

由于两条电缆或引线紧密耦合,因此EMI仅受共模信号的影响。传输过程中的共模变化可以忽略,意味着LVDS即使在非常高的工作频率下也具有非常低的辐射。此外,在350mV低差分电压摆幅在100终端电阻上仅消耗1.2mW功率,该数值保持固定,与数据速率无关。与功耗较高的单端信号(如CMOS和TTL)相比,LVDS信号的突出优势是具有极低功耗。

失效保护功能

大多数LVDS接收器都需要具有内部或外部失效保护电路,以便在特定链路状态下或出现故障时接收器的输出能具有一个已知状态,通常为逻辑高电平。以下列出了需要失效保护的链路状态或故障。

输入开路:如果LVDS芯片具有多个接收端口,则未使用的接收器输入必须保持开路状态,且输出应为稳定的逻辑高电平。

输入浮空:如果LVDS驱动器处于三态、驱动器断电或链路断开,LVDS必须具有稳定的逻辑高电平输出。

输入短路:如果两条平行LVDS电缆或引线短路,即出现连接故障,输出应为逻辑高电平。

设计人员还希望即使在噪声环境下也具有强大的失效保护功能,并要求它对正常状态下的LVDS工作影响最小,可忽略不计。

失效保护电路及其性能分析

这里给出了三种基本的失效保护电路:外部偏置电路、内部通道电路以及并联电路。下面将逐一介绍这些失效保护电路的工作原理,并分析各自的优缺点。

外部偏置失效保护电路

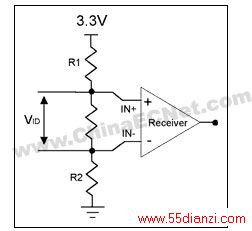

该失效保护电路由接收器输入引脚的三个外接电阻组成(图3)。

图3. 外部失效保护电路

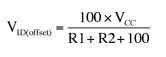

在上述电路中,线路未被驱动时,偏置电路设置两个输入引脚之间的正偏移电压,以便接收器输出处于逻辑高电平。偏移电压VID可由下式决定:

电路的共模电压由下式确定:

![]()

例如:若要在浮空的电路上获得50mV的VID偏移量,需要选择R1 = 4170、R2 = 2450。假定噪声幅度小于VID偏移量,则接收器输出处于逻辑高电平。

该失效保护电路已广泛用于早期的LVDS接收器。由于具有下列优势,所以成为首选方案:

可按照浮空传输线的噪声电平灵活设置偏移电压。

提供了一个共模返回通道和一个ESD放电通道。

但是,这种方法还存在以下几个缺点,限制了它在目前LVDS应用中的使用:

两个必要的外部电阻对于单个LVDS链路可能不是负担,但在采用多个链路时,特别是多通道应用中,就需要认真考虑。

目前,计算机外设和网络互连的LVDS数据传输速率达到800Mbps,甚至2Gbps。在如此高的数据速率下传输,由VID偏移量造成的不平衡接收门限会导致占空比严重失真,并增大抖动。

由于VID偏移不能设置过高,因此对于差分噪声的失效保护具有较低余量。

输入短路时该电路不起作用。电源短路时,VID偏移电压也被短路,LVDS输出不确定。

内部通道失效保护电路

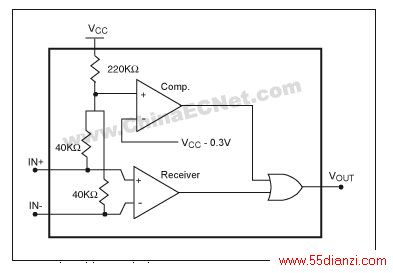

内部通道失效保护电路的设计与外部偏置电路类似,只是该电路将R1和R2集成在LVDS接收器内部,使VID的偏移量成为一个内置电压源。这种电路已广泛用于LVDS接收器[2],图4给出了等效电路。

图4. 内部通道失效保护电路框图

进行内部通道电路设计时,选取R1和R2的值,使VID的内部偏移量在30mV与50mV之间。即使输入短路,仍有正的VID偏移,这样,在上述三种状态下或需要失效保护时,都能够将输出置为逻辑高电平。

这种内部通道设计方法优于外部偏置电路,因为它克服了后者的一些缺点。内部通道失效保护电路的特性如下:

无需外部电阻。

输入短路时仍具有保护功能。

虽然如此,内部通道失效保护在某些应用中仍具有一些缺点:

不具有设置电压偏移的灵活性。

产生了一个不平衡的接收器门限,使占空比降低,抖动增加。

对“内部通道” 噪声具有较低余量。

并联失效保护电路

Maxim的大多数LVDS产品采用了并联失效保护电路[3]。该电路克服了前两种失效保护电路缺点,如图5所示。

图5. 并联失效保护电路原理图

本文关键字:暂无联系方式电子技术,电工技术 - 电子技术