低相噪高纯谱数字捷变频合器的实现

点击数:7325 次 录入时间:03-04 11:49:30 整理:http://www.55dianzi.com 电子技术

DAC的非理想特性,阶梯波在DAC输出端产生谐波与杂散分量。在本系统中DDS芯片使用ADI公司的AD9854作为其核心,相位截短引起的杂散可忽略不计,量化误差可根据实际的波形带宽,采用过采样技术加上滤波获得更高信噪比。DAC的非理想特性,在实际使用中只能选择具有良好线性度的DAC来改善DDS输出信号质量。

实验结果

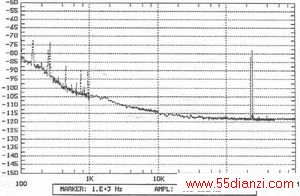

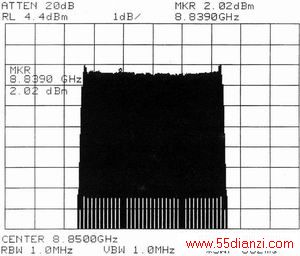

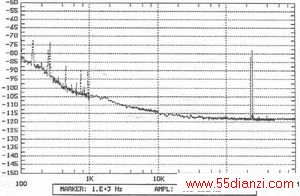

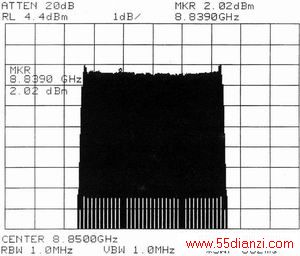

按照图1所示框图完成的X波段频率合成器本振路单边带相位噪声功率谱密度曲线(fo=9500MHz)如图5所示,发射路带宽为50MHz线性调频信号波形如图6所示。

图4 DDS功能方框图

图5 单边带相位噪声功率谱密度曲线

图6 50MHz线性调频信号波形

上一页 [1] [2] [3] [4]

本文关键字:暂无联系方式电子技术,电工技术 - 电子技术