列车运行监控记录装置已在铁路的安全运输过程中发挥了巨大的作用,其不足之处是没有音频、语音记录功能。为了解决这个问题,按照铁道部的技术要求,研究开发了一种新型列车音频、语音记录设备。该设备主要用于协同监控装置分析行车事故,运用相关技术记录设备运行的状态信息,以及对乘务员机车联控进行录音,为机务部门和运输部门的科学管理提供新的技术手段。鉴于常见设备的技术指标及技术标准,对于音频的数字化,以44.1kHz的采样频率、16bit的量化精度进行采样,在编码方面,采用 MPEG I-LayerⅡ压缩编码方式;对于语音的数字化,以16kHz的采样频率、16bit量化精度进行采样,在编码方面,采用MPEG-2压缩编码方式。

1 硬件 系统 组成

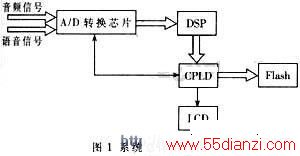

该监控记录设备总体结构如图1所示,整个系统由A/D转换芯片、数字信号处理器DSP、CPLD控制器、Flash大容量存储器及LCD显示屏等组成。

在本系统中A/D转换芯片用来完成信号的转换,数据格式在16、18、20bit之间可选;数字信号处理器(DSP)为系统的核心数字处理器,功能强大,完成数字信号的压缩编码;CPLD用于数据传送的控制以及对A/D转换器、Flash存储器和LCD显示屏等器件的初始化检测设置;Flash大容量存储器用来进行数据的存储;LCD显示屏用来显示当前系统所处的状态,如运行等待、数据处理等。系统上电后,若有音频/语音信号输入A/D转换器,通过中断、查询判断输入的信号类别,之后进行音频/语音信号的模拟/数字格式转换,得到的一串数字信号送入DSP进行数据压缩编码后,经由CPLD存储到Flash大容量存储器中。整个系统以流水线的方式工作,数据的采集、压缩编码、存储同时进行。

1.1 音频/语音处理器UDA1341TS

UDA1341TS是由Philips公司生产的一款单片立体声A/D、D/A转换器,低功耗,工作电压3.0V,信噪比为97dB,具有双通道输入功能,采样频率在16kHz、32kHz和44.1kHz之间可选。

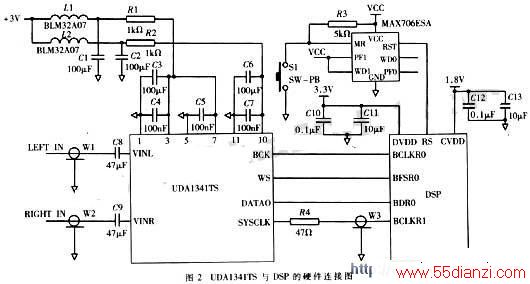

UDAl341TS与DSP构成音频/语音信号采集系统,主要涉及到位采样时钟(BCK)、字同步时钟(WS)、采样数据输出(DATA0)、系统时钟输入(SYSCLK)这几个对时序有要求的引脚。系统中,DATA0作为输出引脚,与DSP的BDR0引脚相连;BCK、WS、SYSCLK作为输入引脚,其时序由DSP供给。UDA1341TS的系统时钟只能是256Fs、384Fs、512Fs,通过对状态寄存器的SC0位和SC1位编程可实现系统时钟的选择设置。这里Fs是音频/语音信号的采样频率。在数据采样时,WS用来指明UDA1341TS的DATAO输出的有效数据。当系统对VINL(左声道)端口进行采样时,WS的上升沿表明一帧数据的起始,下降沿表明一帧数据的结束;当系统对VINR(右声道)端口进行采样时,WS的下降沿表明一帧数据的起始,上升沿表明一帧数据的结束。

UDA1341TS提供了一个L3端口,利用CPLD控制器对L3的L3DATA、L3MODE、L3CLOCK三个引脚进行编程,可以设置其内部的寄存器。当L3MODE引脚为低电平时,通过L3DATA引脚输入寄存器地址信息;当L3MODE引脚为高电平时,通过L3DATA引脚输入有关寄存器设置的数据信息(如设置芯片系统时钟频率、数据输入格式、芯片工作模式等)。UDA1341TS与DSP的McBSP(多通道缓冲同步串口)相连,各种同步信号由DSP产生,这样就保证了新数据的正常接收以及已接收数据的正常处理。UDA1341TS与DSP的硬件连接图如图2所示。

1.2 音频/语音编码器TMS320VC5402

数字音频/语音信号的压缩需要大量的数字信号处理,一般单片机是无法完成的,所以本系统中选用TI公司的DSP芯片TMS320VC5402(以下简称‘C5402)对音频/语音信号进行压缩处理。‘C5402是TI公

www.55dianzi.com

司于1999年10月推出的54X系列定点DSP,操作速率达100MIPS,具有增强的多总线结构,三条独立的16位数据存储器总线和一条程序存储器总线;40位的算术逻辑单元,包括两个独立的40位累加器、17位×17位的并行乘法器和一个40位的桶形移位器;支持单指令循环和块循环,存储块移动指令提供了高效的程序和数据存储器管理,支持并行存储和并行加载的算术指令、条件存储指令和中断快速返回,支持定点DSP C语言编译器。

C5402通过它的多通道缓存串行口(McBSP)与音频/语音处理器UDA1341TS通信。McBSP提供了全双工的通信机制以及双缓存的发送寄存器和三缓存的接收寄存器,允许连续的数据流传输,数据宽度在8、12、16、20、24、32比特之间可选;McBSP与音频/语音处理器的通信通过BDRO引脚实现,通信过程的控制则由BCLKRO、BCLKR1、BFSRO等三条引脚实现。

1.3 CPLD低速控制

DSP作为高速的运算处理器不适合低速的控制应用。本 系统 中对UDA1341TS检测、初始化,对液晶显示LCD的控制以及对Flash的存储控制都是一些低速的控制。本系统采用ALTEra公司的EPM7128S CPLD来完成这些工作,这样就给系统的编程调试带来了极大的方便,缩短了开发周期。

2 运行软件开发

软件设计方面主要包括音频/语音数据的压缩编码以及音频/语音数据的差错校验。

2.1 音频/语音数据编码

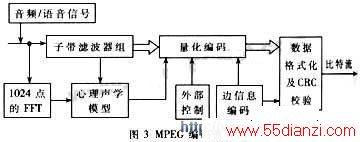

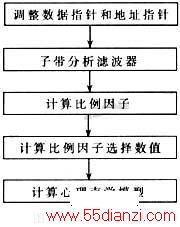

音频编码算法方面采用了目前通用的 MPEG I—Lay-erII压缩编码算法,该算法是帧数据结构编码,一帧的样点值是1152,以处理器件UDA1341TS的44.1kHz采样频率计算,一帧数据的编码要求在26ms内完成。语音编码算法方面采用了MPEG-2压缩编码算法。MPEG-2算法是MPEG-I算法的扩展,一帧的样点值是576,以处理器件UDA1341TS的16kHz采样频率计算,一帧数据的编码要求在72ms内完成。而‘C5402的指令周期是10ns,对于这里的MPEG算法,在满足算法要求的情况下,进行双通道的实时编码最多需要15ms,所以‘C5402可以完成算法的实时编码。其算法流程如图3所示,主要包括以下几方面:(1)滤波器组的运算。(2)心理声学模型的运算。(3)量化编码。(4)帧数据格式化。

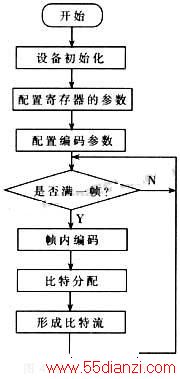

滤波器组的作用是完成信号从时域到频域的映射。心理声学模型的计算是利用1024点的FFT,对输入的音频/语音信号进行频谱分析,再结合时频映射的结果,计算出各子带人耳的掩蔽特性。量化编码是由各子带人耳的掩蔽特性和输出比特率的要求,计算出各子带编码所需的比特分配信息,并且对各子带数据进行线性量化编码的过程。程序的后续工作是按照MPEG标准对数据进行格式化,其目的是为了使数据编码后能被正确地解码。系统主程序流程图如图4所示。

帧内编码是DSP按照MPEG标准把A/D转换器传来的数字音频/语音信号进行压缩编码。其流程如图5所示。

2.2 数据的差错校验

2.2.1 校验原理

音频,语音数据的差错校验采用循环冗余CRC-16校验方式,即被处理的数据块可以被看作是一个N阶的二进制多项式D(X),如一个16位二进制数1010010110100101可以表示为:X15+X13+X10+X8+X7+X5+X2+1。多项式乘除法与普通代数多项式的乘除法运算相同,多项式的加减法以2为模,进行逻辑异或运算。采用CRC校验时,发送方和接收方采用同一个生成多项式S(X),并且S(X)的首位和最后一位的系数必须为1,本算法中S(X)采用多项式。CRC的处理方法是:发送方以生成多项式S(X)去除待处理的数据D(X),得到余数作为CRC校验码。校验时,以计算的校正结果是否为0来判断

www.55dianzi.com

数据帧是否出错。

2.2.2 校验算法实现

本文关键字:监控系统 交通控制指示,应用领域 - 交通控制指示