(

www.55dianzi.com

�۲�wire

ͬ���ģ���SignalTap II�۲�wireʱ����ʱҲ����Ϊ��QUARTus II�Ż���������SignalTap II�۲졣

SignalTapII_wire_not_keep.v / Verilog

- module SignalTapII_wire_not_keep (

- input ICLK,

- input iRST_N,

- output [3:0] oCNT

- );

- wire [3:0] Cnt;

- reg [3:0] cnt;

- assign Cnt = cnt;

- assign oCNT = Cnt;

- always@(posedge iCLK, negedge iRST_N) begin

- if (!iRST_N)

- cnt <= 4'h0;

- else

- cnt <= cnt + 4'h1;

- end

- endmodule

7��

wire [3:0] Cnt;

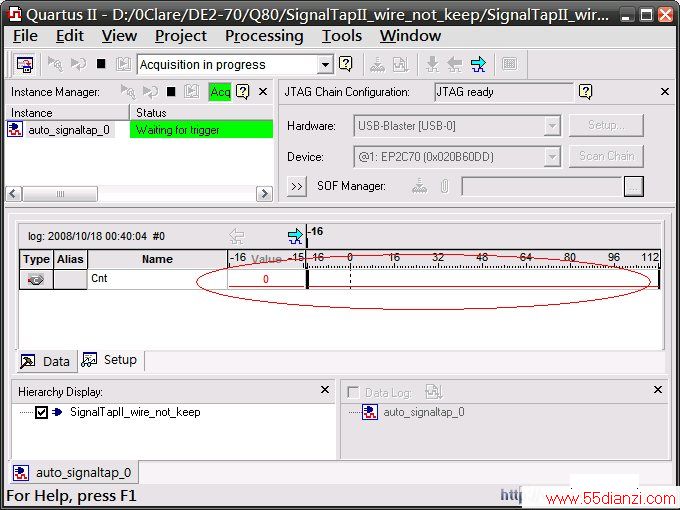

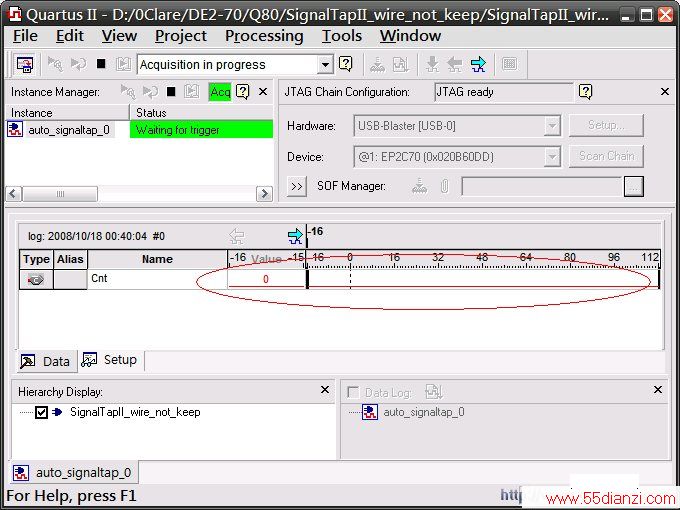

����������SignalTap IIȥ�۲�Cnt���wire��

Cnt����0����Ȼ����������ʾSignalTap II��capture cnt���wire��ֵ��Ϊʲô��������?

��ΪCnt���wire�Ѿ���Quartus II�Ż�������!!

������ʱΪ��debug���㣬���Ǿ�����۲�����wire���а취��Quartus II��ʱ��Ҫ������ѻ���?

SignalTapII_wire_keep.v / Verilog

- module SignalTapII_wire_keep (

- input iCLK,

- input iRST_N,

- output [3:0] oCNT

- );

- wire [3:0] Cnt /*synthesis keep*/;

- reg [3:0] cnt;

- assign Cnt = cnt;

- assign oCNT = Cnt;

- always@(posedge iCLK, negedge iRST_N) begin

- if (!iRST_N)

- cnt <= 4'h0;

- else

- cnt <= cnt + 4'h1;

- end

- endmodule

7��

wire [3:0] Cnt /*synthesis keep*/;

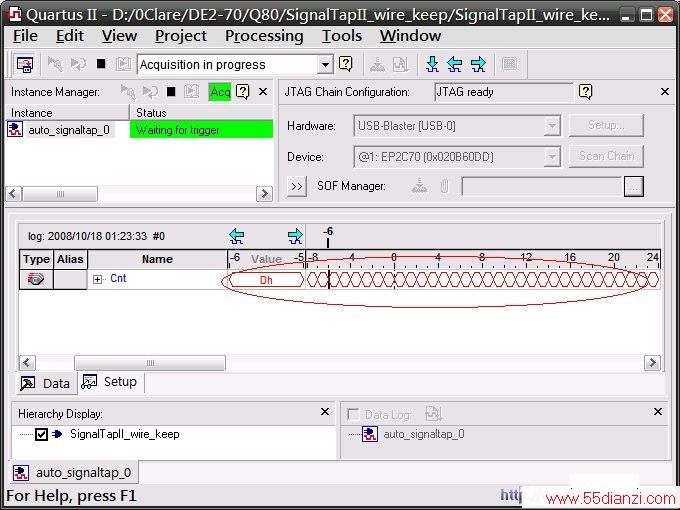

����/*synthesis keep*/���synthesis attribute��ָʾQuartus II��Ҫ��Cnt����ѻ���������wire�Թ�SignalTap II�۲죬ע�����д�ڷֺ�ǰ�棬��������д�ڷֺź��档

wire [3:0] Cnt;/*synthesis keep*/ //��

�����SignalTap II����˳���Ĺ۲쵽Cnt��ֵ!!�ص��Dz����top module��interface��ֻ�����۲��wire����synthesis attribute���ɡ�

Quartus IIҲ֧ԮVerilog 2001���Z��

- module SignalTapII_wire_keep (

- input iCLK,

- input iRST_N,

- output [3:0] oCNT

- );

- // Verilog 2001

- (*keep*) wire [3:0] Cnt;

- reg [3:0] cnt;

- assign Cnt = cnt;

- assign oCNT = Cnt;

- always@(posedge iCLK, negedge iRST_N) begin

- if (!iRST_N)

- cnt <= 4'h0;

- else

- cnt <= cnt + 4'h1;

- end

- endmodule

8��

(*keep*) wire [3:0] Cnt;

����Verilog 2001�����Quartus II 8.0Ҳ�ܿ��ö���

����

���ڱ���Quartus II�Ż�reg��/*synthesis noprune*/��/*synthesis preserve*/������Щ���죬����д���ܴ�ʱ������һʱ���Ѿ���Ҫ����һ��attribute�����Խ������Կ�������1/2�Ļ��ᣬ�ܻ��һ������ʹ��synthesis attribute֮����������������������SignalTap II�۲�reg��wire�������⡣

�۲�wire

ͬ���ģ���SignalTap II�۲�wireʱ����ʱҲ����Ϊ��QUARTus II�Ż���������SignalTap II�۲졣

SignalTapII_wire_not_keep.v / Verilog

- module SignalTapII_wire_not_keep (

- input ICLK,

- input iRST_N,

- output [3:0] oCNT

- );

- wire [3:0] Cnt;

- reg [3:0] cnt;

- assign Cnt = cnt;

- assign oCNT = Cnt;

- always@(posedge iCLK, negedge iRST_N) begin

- if (!iRST_N)

- cnt <= 4'h0;

- else

- cnt <= cnt + 4'h1;

- end

- endmodule

7��

wire [3:0] Cnt;

����������SignalTap IIȥ�۲�Cnt���wire��

Cnt����0����Ȼ����������ʾSignalTap II��capture cnt���wire��ֵ��Ϊʲô��������?

��ΪCnt���wire�Ѿ���Quartus II�Ż�������!!

������ʱΪ��debug���㣬���Ǿ�����۲�����wire���а취��Quartus II��ʱ��Ҫ������ѻ���?

SignalTapII_wire_keep.v / Verilog

- module SignalTapII_wire_keep (

- input iCLK,

- input iRST_N,

- output [3:0] oCNT

- );

- wire [3:0] Cnt /*synthesis keep*/;

- reg [3:0] cnt;

- assign Cnt = cnt;

- assign oCNT = Cnt;

- always@(posedge iCLK, negedge iRST_N) begin

- if (!iRST_N)

- cnt <= 4'h0;

- else

- cnt <= cnt + 4'h1;

- end

- endmodule

���Ĺؼ��֣�������ϵ��ʽ����-��Ƭ��-�Զ�����������ѧϰ - ����֪ʶ - ����-��Ƭ��-�Զ�����