电平移位电路是将低压控制信号转换为高压控制信号,实现低压逻辑对高压功率输出级的控制,属于高压器件的控制技术领域,该种电路在电机驱动、PDP显示、OLED显示等方面得到了广泛的应用。

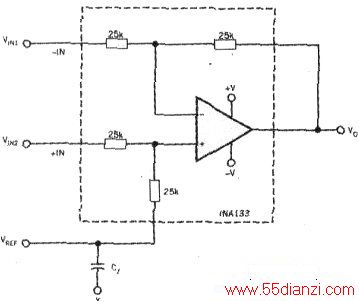

不少电路采用运算放大器和1%公差的分立电阻器制作电平移位器。分立电阻器失配,会将运算放大器的CMRR(共模抑制比)限制在40dB以下,所以不能在要求CMRR很高的电路中使用运算放大器。差分放大器包含精密匹配的内部电阻,所以诸如INA133等lC均自暂艮容易地达到大约90dB的CMRR。只要微调内部的匹配电阻,它们均具有这样高的CMRR。附图所示电路的每个输入端,都有相关噪声电压(VN1、VN2和VNREF)。放大器电路的传输函数是VOUT= (VREF十VNREF)+ (VIN2+VN2)-(VIN1+VN1)。由于基准电压会使单一的输出信号或差分输出信号发生电平移位。一旦发生这种电平移位,就应消除噪声。

只要精心布线,只要将信号差分耦合到差分放大器输入端,就能使信号输入端的噪声相等(VNI=VN2)当输入噪声是共模信号时,差分放大器就能最大限度地予以抑制(通常可抑制90dB)。这时,VOUT=VIN2-VINI+VREF+VNREF。

为了消除基准噪声,可把CI的X端连接到信号源V1N1,差分放大器就起低通滤波器的作用,从而抑制基准源噪声。这一电路使差分放大器的输入阻抗很低(INA133约为25kΩ),以利于阻抗匹配。因此,必须保持信号源阻抗很低,以防止增益误差。为将增益误差降至最低程度,信号源阻抗应该低于输入阻抗的1/1000。

如果无法实现这钟情况,那么最好要对输入信号进行缓冲。

本文关键字:暂无联系方式变换电路,单元电路 - 变换电路

上一篇:基于三极管的电平转换及驱动电路