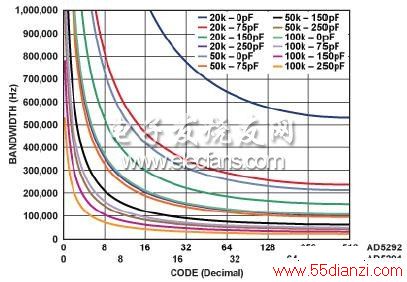

图8.各种电阻值的最大带宽与负载电容

PC板的寄生走线电容也应加以考虑,否则最大带宽会低于预期值,走线电容可以采用以下公式简单计算:

其中

&epSILon;R是板材的介电常数

A是走线区域(cm2)

d是层间距(cm)

如,假设FR4板材有两个信号层和电源/接地层, εR = 4, 走线长度 = 3 cm宽度 = 1.2 mm, 层间距 = 0.3 mm; t则总走线电容约为 4 pF.

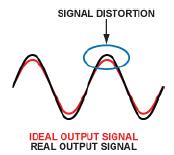

失真

THD用于量化器件作为衰减器的非线性。该非线性由内部开关及其随电压变化的导通电阻 RON而产生。图9所示为放大的幅度失真示例.

图9.失真

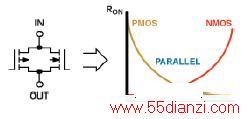

与单个内部无源电阻相比,开关的RON很小,其在信号范围内的变化则更小。图10显示的是典型的导通电阻特性。

图10.CMOS电阻

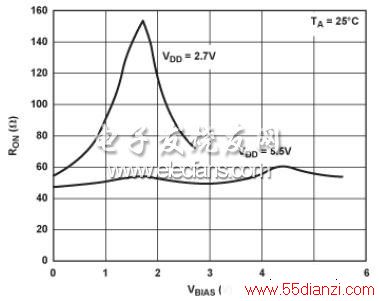

电阻曲线取决于电源电压轨,电源电压最大时,内部开关的RON 变化最小。电源电压降低时,RON 变化和非线性都会随之增加。图11对比了低压digiPOT在两种供电电平下的 RON

HD取决于各种因素,因此很难量化,若假设RON,的变化为10%,则以下公式可用于近似计算:

一般说来,标称digiPOT电阻 (RPOT),越大,则分母越大,THD就越小.

权衡

RPOT增加后,失真和带宽都会随之降低,所以改进一项指标的同时必定会牺牲另一项。因此,电路设计人员必须在两者之间做出适当的权衡。这也关系到器件的设计水平,因为IC设计人员必须平衡设计公式中的各个参数:

其中

COX 是氧化电容

μ 是电子(NMOS)或空穴(PMOS)的迁移常数

W是宽度

L是长度

偏置

从实用的角度来看,我们必须充分发挥各项特性。digiPOT通过容性耦合衰减交流信号时,若信号偏置达到电源的中值,则失真最小。这意味着开关工作在电阻特性线性最强的部分.

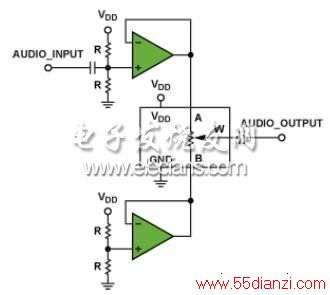

一种方法是采用双电源供电,只需将电位计接地至电源共模端,信号便会产生正负向摆动。如果需要单电源供电,或者某些digiPOT不支持双电源时,可以采用另一种方法,即添加 VDD/2 的失调电压至交流信号。该失调电压必须添加到两个电阻端,如图12所示。

图12.单电源供电交流信号调理

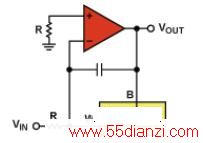

若需要使用信号放大器,双电源供电的反相放大器优于同相放大器(如图13所示),原因有以下两项:

THD性能更佳,因为反相引脚的虚地可将开关电阻集中在电压范围中间。

因为反相引脚位于虚地,所以几乎取消了游标电容CDLSB,令带宽增幅较小(必须注意电路稳定性).

图13.采用反相放大器digiPOT可调整放大

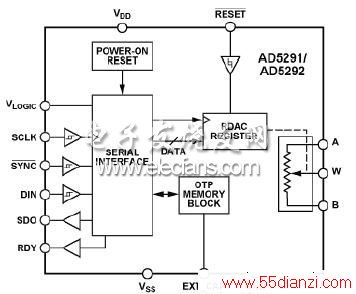

附录——关于AD5291/AD5292

256/1024位数字电位计精度为1%,可编程20次

AD5291/AD5292数字电位计,如图14所示,具有256/1024位分辨率。端对端电阻有20 kΩ、50 kΩ和100 kΩ可供选择,误差优于1%,温度系数在可变电阻器模式下时为35 ppm/°C,分压器 模式下时为5 ppm/°C(比率)。这些器件可实现与机械电位计相同的电子调整功能,但尺寸更小且更可靠。其游标位置可通过SPI兼容接口调整。在熔断熔丝,将游标位置固定(此过程类似于将环氧树脂涂在机械式调整器上)之前,可进行无限次调整。“去除环氧树脂”过程最多可以重复20次。AD5291/AD5292采用9 V至33 V单电源或±9 V至±16.5 V双电源,功耗8 μW。采用14引脚TSSOP封装,工作温度范围为–40°C至+105°C

图14.AD5291/AD5292功能框图

本文关键字:规格 数字电位器,单元电路 - 数字电位器

上一篇:基于光耦电路的线性压控电位器