由于地址和数据总线上的状态不断变化,所以在对LED屏进行写操作时,地址和数据信号应进行锁存,主控板上分别使用U2、U3和U4锁存对LED写操作时的地址和数据总线的状态。LED屏分配首址为Ox2000000,当对其进行写操作时,S3C44BOX的nGCSl和nWE脚会出现可编程控制时延的有效低电平。nGCSl经一个非门作U2、U3和U4的锁存使能控制信号,保证仅在对LED屏访问时,地址和数据总线上的信号才被锁存。nWE经一个非门作屏端第一级列数据锁存器(图1中U3~U19)的锁存使能控制信号,保证只有当刷新数据稳定出现在列数据锁存其输入端时才被锁存。S3C44BOX的PCI0作所有屏端第二级锁存器(图1中U20~U35)的锁存使能控制信号线;S3C44BOX的PC[3:O]作16行驱动译码器(图1中U1)的译码输入。由于数据传输时只需要主控板对LED屏输出控制,不需要信号反馈,所以接口电路采用廉价的5V供电的HCT电路芯片方案,就可满足主控芯片3.3V到LED屏5V的逻辑电平转换。

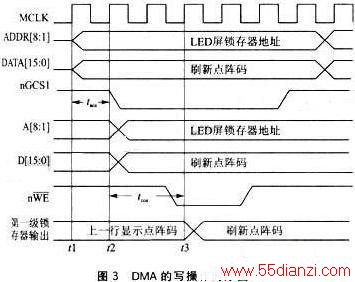

在DMA传输数据时,更关心的是DMA的写操作,时序如图3所示。t1时刻DMA写操作开始,地址和数据总线上出现LED屏相应位置的地址和刷新数据;t2时刻nGCS1引脚出现有效低电平,地址和数据总线上的数据被锁存到U2~U4并输出;t3时刻nWE引脚出现有效低电平,U2~U4的输出数据被锁存到屏端第一级列数据锁存器并输出。这样主控制器就完成了一次列数据的刷新。

2 软件设计

2.1 LED屏显示程序设计

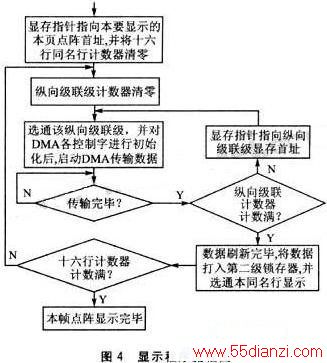

由于使用了S3C44B0X内部DMA控制器进行数据的传输与控制,显示程序得到很大简化,程序流程如图4所示。点阵码的传输全由DMA控制器完成,只需在启动DMA数据传输前将点阵码的首址、LED屏的首址及传输数据量的值分别赋给相应的控制字后,启动DMA操作即可。完成所有本同名行点阵码传输后,将刷新的数据锁存到第二级列数据锁存器输出,并驱动本同名行显示。这样循环显示16行同名行后就完成了一帧点阵显示。

2.2 点阵排序

由于LED显示模块的电路结构以及使用了16位并行总线和DMA数据传输技术,在显示时点阵码的排放顺序,需要满足如下要求:

①16位并行总线一次数据传输,即一次DMA写操作传输两个字节的点阵码,低位和高位字节分别传送到两相邻的纵向级联模块的同名行和同名列数据锁存器中,因此相邻的纵向级联模块的同名行和同名列点阵码应连续存放。

②由于显示模块的第一级列数据锁存器译码选通电路结构和DMA数据传输要求,对同一显示模块的上下两部分的同名行点阵应按列数据锁存器的选通顺序依次连续存放。

③两相邻的纵向级联级的一系列横向级联级应按①和②原则进行点阵码排序。

本文关键字:暂无联系方式显示电路-显示屏,单元电路 - 显示电路-显示屏