内容摘要:由FPGA控制视频译码芯片ADV7170,接收来自红外热像仪输出的数字图像,从而把数字图像转化为PAL制模拟信号并由电视机进行显示。该红外数字图像显示系统具有小型化、低功耗、灵活性强等特点,能够广泛应用于国防科技中。

关键词 FPGA;ADV7170;数字图像

ADV7170芯片是AD公司推出的一款较新且功能较强的视频译码器,这款高度集成的芯片,既包含精密的模拟电路,又包含高速数字电路。ADV7170应用广泛,适用于DVD播放器、便携式视频设备、视频监视器和机顶盒等场合。

红外热像仪将物体表面的温度转换成人眼可见的图像,并以不同灰度值显示物体表面的温度分布。红外热像仪具有超远距离成像特点,成像距离主要由物体温度决定,从而克服传统成像器件成像距离短的弊端。文中利用这一特点实现对热像仪周围空域的实时监测,达到预警的效果。

1 设计方案

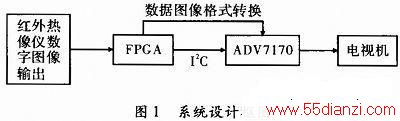

文中嵌入式数字图像显示系统硬件系统结构如图1所示,在此图像显示系统中,采用ALTEra公司的Cyclone 3系列FPGA:EP3C80F484C6,Analog DevICe公司的视频译码芯片ADV7170。首先FPGA使用I2C总线对ADV7170的内部寄存器进行配置,然后FPGA接收来自红外热像仪输出的数字图像,并转化为ADV7170可识别的数据格式,最后由ADV7170把数字图像转化为PAL制模拟信号给电视机显示。

2 ADV7170的配置

Analog Device公司生产的ADV7170是一款通用性强的视频译码芯片。它是一款集成的数字视频译码器,将数字形式的ITU_R_BT656组合视频数据,转换成标准的模拟基带电视信号。它可以同时输出一路复合视频信号及一组RGB信号,或一路复合视频信号及一组YUV信号,或二路复合视频信号及一组亮度与色度信号。ADV7170的数据输入有两种模式:8位与16位。当工作于8位模式时,引脚P7~P0作为数据输入口,输入数据序列为Cb0、Y0、Cr0、Y1、Cb1、Y2……,在每个时钟的上升沿采样数据;当工作于16位模式时,引脚P7~P0输入Y信号,引脚P15~P8输入Cb、cr信号,每两个时钟的上升沿采样数据。无论工作在那种数据输入模式,在输入数据流中都需要嵌入同步控制数据。对该芯片应用的关键就是要设置ADV7170内部的一些寄存器使ADV7170能正常工作。而ADV7170采用了I2C总线接口标准,所以对该芯片的控制就主要是通过I2C总线进行寄存器的配置。

(1)I2C总线的基本原理。I2C总线是Philps公司开发的一种用于芯片间通讯的串行数据传输总线,它由串行时钟线SCLOCK和串行数据线SDATA完成全双工数据传送。串行的8位双向数据传输速率,在标准模式下可达100 kbit·s-1,快速模式下可达400 kbit·s-1,高速模式下可达3.4Mbit·s-1。I2C总线数据传输时,在时钟高电平期间数据线上必须保持有稳定的逻辑电平转态,高电平为数据1,低电平为数据0。只有在时钟线为低电平时,才允许数据线的电平状态变化。发送到串行数据线SDATA线上的每个字节必须为8位,每次传输发送的字节数量不受限制。每个字节后鼻血跟一个相应位,首先传输的是数据的最高为。如果从机要完成一些其他功能后才能接受或发送下一个完整的数据字节,可以使时钟线SCLOCK保持低电平迫使主机进入等待状态。当从机准备好接收下一个数据字节并释放时钟线SCLOCK后,数据传输继续。

I2C总线起始信号:在时钟线保持高电平期间,数据线出现由高电平向低电平变化时启动I2C总线,为I2C总线的起始信号。

I2C总线终止信号:在时钟线保持高电平期间,数据线出现由低电平向高电平变化时停止I2C总线数据传输,为I2C总线的终止信号。

I2C总线应答信号:I2C总线数据传送时,每传送1Byte数据后必须有应答信号。应答信号在第9个时钟位上出现,接受器输出低电平为应答信号,输出高电平则为非应答信号。

图2为ADV7170的I2C总线的一次完整的数据传输。

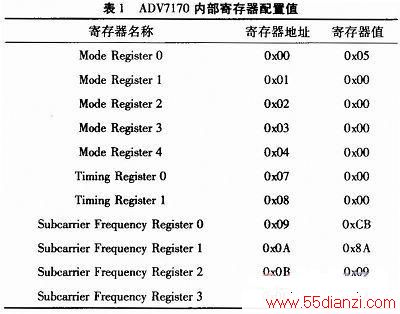

(2)I2C模块设计与VHDL实现。设计需要配置的ADV7170内部寄存器如表1所示。

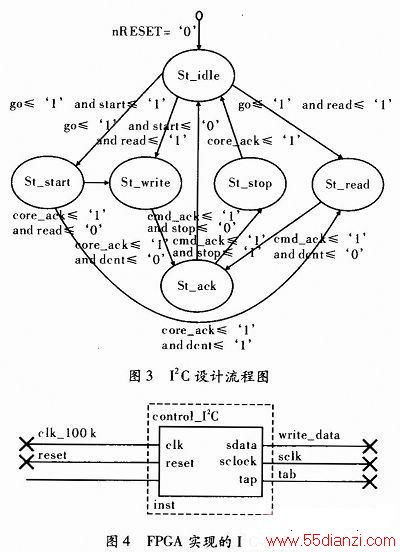

采用状态机方式实现I2C模块的功能,图3所示状态机中有6个状态,分别是St_idle,St_start,St_write,St_read,St_stop和St_ac k。系统复位之后进入St_idle状态,收到go和start命令后进入St_start状态,在St_start状态下判断随后到达的命令,如果是写寄存器命令,则进入写状态;如果是其他命令,则进入相应的状态。每次数据传输完成后会读取ack信号,判断寄存器是否配置完成。如果完成则进入停止状态,由于实际工作中不需要读寄存器的值,所以读命令只在调试中应用到。图4是FPGA实现I2C模块。

如图4所示,用VHDL语言实现了I2C总线对ADV7170内部寄存器的配置,图5~图6为使用中的写时序和读时序图。

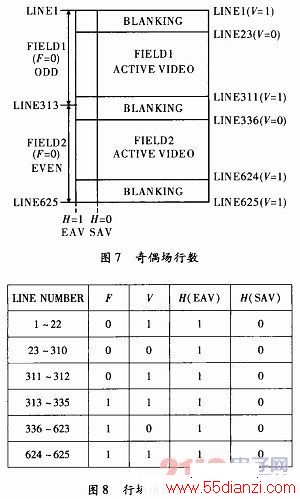

(2)图像数据格式转换。在PAL制模式下ADV7170能接受的图像数据大小为625×1 728,即每帧图像有625行,每行有1 728个像素点,这种格式是国际通用的TTU_R_BT656视频图像格式。ITU_R_BT656定义了一个并行的硬件接口,用来传送一路4:2:2的YCbCr数字视频流和行场所用的控制信号。ITU_R_BT656视频图像格式分为奇场和偶场,奇场313行,偶场312行,每场均有24个消隐行,如图7所示。每行有行开始状态位SAV,行结束状态位EAV,每行对应的场信号F,行信号H,消隐信号V如图8所示。根据BT_656的这种格式特点需要对接受到的红外数字图像进行格式变化。红外热像仪输出的数字图像大小为256×320,即每帧图像有256行,每行有320个像素点。按照数字图像的大小,每行里的每个像素点连续读取4次,奇场和偶场各读取一次图像。即完成图像的扩展,剩余的像素元素使用消隐值进行替代。

FPGA实现上述格式转换过程:将一帧数字图像存入FPGA内部的双口RAM中,由于ADV7170工作在27 MHz时钟频率,所以需要设置一级乒乓缓存操作。乒乓操作是一个常常应用于数据流控制的处理技巧,典型的乒乓操作方法如图9所示。乒乓操作的处理流程描述如下:输入数据流通过“输入数据流选择单元”,等时地将数据流分配到两个数据缓冲模块。在第一个缓冲周期,将输入的数据流缓存到“数据缓冲模块1”。在第二个周期,通过“输入数据流选择单元”的切换,将输入的数据流缓存到“数据缓冲模块2”,与此同时,将“数据缓冲模块1”缓存的第一个周期的数据通过“输出数据流选择单元”的选择,送到“数据流处理模块ADV7170”上。在第3个缓冲周期,通过“输入数据流选择单元”的再次切换,将输入的数据流缓存到“数据缓冲模块1”,与此同时,将“数据缓冲模块2”缓存的第二个周期的数据通过“输出数据流选择单元”的切换,送到“数据流处理模块ADV7170”,依次循环。乒乓操作的最大特点是,通过“输入数据流选择单元”和“输出数据流选择单元”按节拍、相互配合地切换,将经过缓冲的数据流没有时间停顿地送到“数据流处理模块ADV7170”。把乒乓操作模块当作一个整体,站在这个模块的两端看数据,输入数据流和输出数据流连续不断,没有停顿,适合对数据流进行流水线式处理,所以使用乒乓操作完成数据的无缝缓冲与处理,达到低速模块处理高速数据流的效果。设置行计数器,读取每行的像素值,然后将读取的像素值写入ADV7170的数据总线上,最后可以得到ADV7170输出的PAL制模拟信号。下面是数字图像和电视机接收的模拟信号显示图像。

本文关键字:暂无联系方式显示电路-显示屏,单元电路 - 显示电路-显示屏