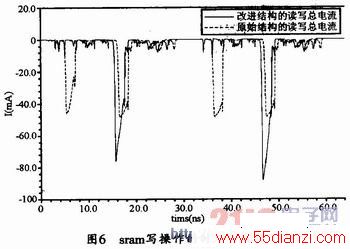

由图6可见,改进结构在写操作时没有大电流,而在读操作时会有部分尖峰电流,这主要是由于平衡预充位线抬高了位线初始电压,从而降低了预充PMOS管的导通电阻所致。

改进SRAM结构的动态功耗为4.6mW。若用传统SRAM结构,对于相同大小的电路,其仿真得到的动态功耗为5.96mW。因此,相比传统结构,改进型结构的动态功耗减小了22.8%。

5 结束语

本文对显示驱动芯片中内置SRAM电路进行了低功耗研究与设计。新方法采用位线划分和字线划分技术来设计SRAM整体结构,从而降低了寄生电容。事实上,结合低功耗位线技术对传统SRAM单元结构进行改进,写操作时停止对位线预充电,可以达到降低功耗目的。而引入仲裁算法可解决SRAM访问的时序问题。根据SRAM读写操作要求设计的时序产生电路的仿真结果显示,其动态功耗可以得到大幅降低。

目前,本电路已经应用在一款AM_OLED显示驱动芯片中,并已完成前期仿真。仿真结果可以达到预期指标要求,从而证明了该电路的可行

性。

本文关键字:暂无联系方式显示电路-显示屏,单元电路 - 显示电路-显示屏