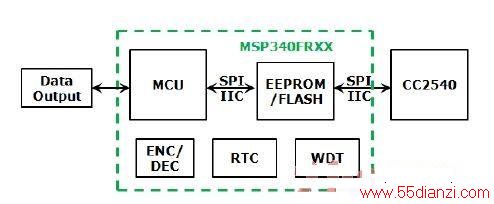

通过优化后的系统框图如下图所示,可以看出使用MSP430FRXX 系列MCU 后,系统的硬件设计得到了优化,同时面对小FLASH,大RAM这样的MCU 选型难题时,获得了很好的解决;再有就是MSP430FRXX 系列MCU 自带的功能强大的RTC,数据加解密,WDT 等功能也提到了系统的集成度和性能。

图2.6 MSP430FRXX 系列MCU 模块化的数据采集与发布系统中的应用

再例如在如下所示的BLE 数据传输系统中,当数据传输量较大时,要选择一颗RAM 非常大的MCU,通常性价比不高。故通常会用到双接口的存储器,这样可以选择数据处理性能更好的MCU 加一个外接的存储器实现。如果使用MSP430FR59XX,则可以实现存储的功能外,还可以同时实现RTC 与外部WDT,提高系统的可靠性。特别是对于需要数据加密的要求时,可以不修改系统硬件,直接实现。

图2.7 BLE 无线数据传输系统

综上可知,MSP430FRXX 系列MCU 设计的多功能双接口存储器,可广泛的应用在有快速数据传输,经常性数据擦写,以及数据加密要求的应用中。其不仅可发挥FRAM速度快已配置的特点,还可给系统带来RTC,外部看门狗,数据加解密等功能。其为系统提供了强大的数据存储吞吐能力,优化了系统硬件设计,增强了系统扩展功能,解决了小FLASH,大RAM 的MCU 选型等问题。

3 系统设计

3.1 系统框图

基于MSP430FR6969 MCU 设计多功能双接口存储器的系统框图如下:

图3.1 基于MSP430FR5969 的多功能存储器系统框图

• 配置内部数字振荡器(DCO)工作在8MHz 最高主频,为MCLK,SMCLK 分别提供8MHz 的时钟源;

• 配置eUSCI_A0,eUSCI_A1 分别工作在SPI 接口从模式,采用MCLK 作为时钟源,最大支持1Mbps 的通信速率;

• 配置eUSCI_B0 工作为I2C 接口从模式,7-BIT 地址,MCLK 时钟源,最大支持100Kbps 的通信速率

• 配置2 个DMA 通道从FRAM存储器传输数据到eUSCI_A0 和eUSCI_A1,实现SPI 接口的数据的接收,无需CPU 参与;

• 配置1 个DMA 通道从FRAM存储器传输数据到eUSCI_B0,实现I2C 接口的数据的接收,无需CPU 参与;

• Port3 配置为GPIO 扩展端口,支持上升/下降沿中断;

• 使能硬件AES 加密模块,实现AES 加密/解密功能;

• 使能TIMERA0 工作在连续模式,利用CCP0 和CCP1 实现2 路WDT 定时器输出;

• 使能ADC 模块,配置TIMERA1 工作在定时器模式触发ADC 采样,实现电压检测功能,最大支持2 个电压点的检测;

• 使能RTC 模块,实现RTC 功能。

3.2 管脚定义

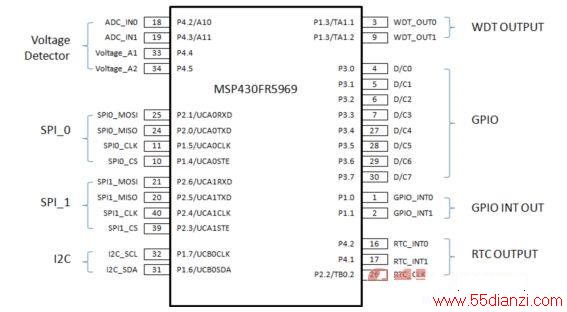

按照3.1 的功能规划,选择40QFN 封装的MSP430FR5969,可对其管脚分配如下。

• 图3.2 MSP430FR5969 引脚分配

3.3 存储器分配

MSP430FR5969 片上支持64Kbytes 的FRAM存储器,其寻址范围为:

0x4400~0x13FFF; 由于MSP430 的复位地址为0xFFFF, 故该地址和中断向量表

把存储器分为两部分: 0x4400~0xFF7F, 0x1000~0x13FFF。

在本文的设计中按照下表来分配FRAM存储器:

根据上表的存储器空间规划可得出存储器分配图,如下图所示:

图3.3 MSP430FR5969 FRAM 存储器分配

MSP430FR5969 的SRAM 存储器容量共有2kBytes,其寻址空间为0x1C00-0x23FF,划分出1K 作为AES 加密/解密模块使用,具体的RAM 空间划分如下:

具体的SRAM 空间功能划分如下图所示:

图3.4 MSP430FR5969 SRAM 存储器分配

3.4 功能模块配置

MSP430FR5969 实现的多功能双接口存储器的各个功能都可以进行使能和配置,其配置参数保留在0xF800~0xFF7F 功能模块配置区。配置寄存器规划如下表:

3.5 系统配置寄存器

功能模块使能寄存器:FUNCITON_EN,基地址0xF800,偏移地址0x0000。该寄存器用来定义本设备使能的功能模块,共16BIT,低8BIT 表示功能模块的使能/关闭。

3.6 I2C 接口说明

系统支持1 路I2C 接口访问。I2C 接口数据格式为7BIT 地址,8BIT 数据,START 信号后的一个字节是设备地址,后两字节为寄存器地址。该接口参照I2C 总线的读写操作规范设计,最高支持100Kbps 的通信速率。

设备共有4 个7 位I2C 设备地址,分别对应4 个不同的功能模块,如下表所示:

各功能模块的寄存器描述详见各功能模块的介绍,I2C 设备地址可根据需

要按照I2C 协议规范规定的器件地址规则更改。

3.7 SPI 接口说明

系统支持最多2 个SPI 接口同时访问,接口SPI0 初始化为开启,接口SPI1可由用户开启或者关闭。

SPI 接口由9 个基本命令字进行操作控制,这9 个基本命令字可以通过SPI总线控制系统。SPI 模式为CS 下降沿启动,MOSI/MISO 上升沿采集,MSB。则MOSI 引脚上数据的第一个字节为命令字,后续字节为数据。

命令字的长度为一个字节,根据其意义与操作不同,后续会有跟随地址字节,数据字节和伪字节。所有的传输必须在CS 引脚的上升沿之前完成,所有的读命令都可以在任意时钟位完成,所有的写、编程、擦除命令在一个字节的边界后才完成,否则命令将不起作用。当芯片正在被编程、擦除或写入状态寄存器的时候,除了“读状态”命令,其它所有的指令都会被忽略直到擦写周期完成。SPI 操作状态寄存器S7~S0 指示当前SPI 操作的状态,用户可以通过读/写状态命令来访问该寄存器。

上一篇:差分信号的有效和故障条件分析