使用功能强大的FPGA来实现一种DDR2 SDRAM存储器的用户接口。该用户接口是基于XILINX公司出产的DDR2 SDRAM的存储控制器,由于该公司出产的这种存储控制器具有很高的效率,使用也很广泛,可知本设计具有很大的使用前景。本设计通过采用多路高速率数据读写探作仿真验证,可知其完全可以满足时序要求,由综合结果可知其使用逻辑资源很少,运行速率很高,基本可以满足所有设计需要。

现如今,随着电子技术和通信技术的飞速发展,电路设计对存储器的要求也越来越高,其主要体现在对存储器的容量和存储操作速度两个方面。鉴于此,JEEDEC定义了DDR2SDRAM技术标准,其以低能耗、低发热量、高密度以及高频率成为了现代存储技术的核心器件。DDR2自身的工作频率可以达到677 MHz,几乎可以满足所有电路设计的要求。而这也就使得整个电路设计的频率瓶颈出现在了用户设计部分与DDR2存储器之间的逻辑上,主要是因为DDR2本身的结构特性使得DDR2的操作时序很复杂苛刻。而这之间的部分又主要分为DDR2存储控制器和用户接口部分。现如今已经有了很多的厂家在生产DDR2存储控制器,其中以XILINX公司设计的DDR2存储控制器效率最高使用最为广泛,该存储控制器的单独操作频率非常高,完全不会影响DDR2存储器的操作,因此这又将整个电路系统的频率瓶颈缩小到了用户接口部分。用户接口的设计有很多种方案,而FPGA以其高速度、丰富的片上资源、灵活的设计以及简单方便的调试特性成为了用户接口设计的必然选择。

1 DDR2存储器应用的一般模式

DDR2存储器一般作为片上系统的辅助器件,其应用的一般模式如图1所示。

用户设计部分是整个片上系统的核心,主要是完成系统要实现的所有任务,对整个系统进行整体的调度和控制。

用户接口部分主要是接收用户设计部分传送的操作数据,以及与这些操作数据相对应的控制指令,之后将这些数据进行整理,然后按照一定的时序要求发出。如果操作的是多路不同种类的数据时,则还要将这多路数据进行仲裁,保证所有数据都不会被发错或者丢失。

DDR2存储控制器主要是接收用户接口部分发给的特定的读写操作控制指令和已经整理好的数据,将这些指令进行进一步的解析,最后将经过解析产生的那些DDR2存储器硬件可以识别的信号以及与读写有效信号有关的写数据输出给DDR2,读数据从DDR2存储器中读回。

DDR2存储器主要是按照读写有效信号将要处理的数据进行读出和写入操作。

2 用户接口设计

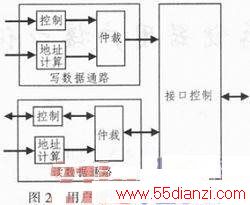

用户接口设计的原理如图2所示。

其主要包括写数据通路、读数据通路以及接口控制3大模块。

写数据通路按照输入存储器路数的不同分为以下两种:只有一路数据输入时只有控制模块和地址计算模块;当有多路数据输入时,不仅有控制模块和地址计算模块还有仲裁模块。

控制模块主要是将输入的数据进行一次2乒乓操作的缓存,再将缓存后的数据拼接成64位数据,之后在仲裁模块允许该路数据写操作时将这些数据发送给仲裁模块。

地址计算模块主要是计算每路信号的每个数据的存储地址,由于每路数据都是不同数据类型的,因此必须要将每路地址的计算与其数据严格地对应起来,要正确的保存好每次写数据操作的地址,以便产生下次操作的正确地址。

仲裁模块主要是保证多路数据对DDR2控制器的访问可以正确进行。DDR2存储控制器采用的是高效的burst操作(对于本设计采用的是burst为30),也就是在一次读操作或者是写操作的过程中要连续处理burst长度所定义的数据个数(在本设计中每次读写操作要完成30个64位数据的读出或写入)。这样在一次请求操作被响应之后,在接下来的15个周期只能传输这路数据,在将这路数据传输完成之前不能再响应其他路数据的操作请求,这样就有可能导致其他多路数据的操作请求在本次操作结束之后同时到来,这样就要求仲裁模块必须要很好地控制每路数据之间的操作顺序,使得多路信号对存储器的访问机率大致相同。鉴于此,本设计中采用了轮询的机制。

读通路和写通路基本类似,只是读通路不需要对数据进行拼接,相反的需要对数据进行拆分,将DDR2存储器输出的64位数据拆分成原始输入时的数据,并将这些数据存入读操作端的FIFO中。这样在外部请求数据数据时,若要求的数据已经在FIFO中则直接将数据输出即可,不需要再向DDR2存储控制器请求,若要求的数据还没在FIFO中则要先向DDB2存储控制器请求数据,将数据存入该FIFO,之后再将FIFO中本次要求读出的数据输出。

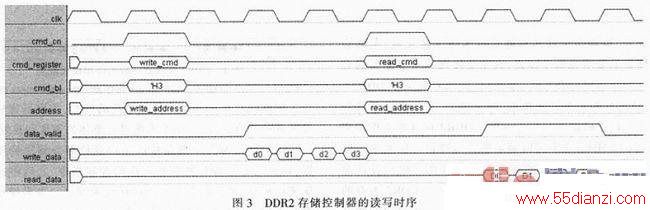

接口控制模块主要是接收写通路的写操作请求信号以及它对应的地址信号和数据信号,读通路的读操作请求信号以及它对应的地址信号,并将这些信号按照DDR2存储控制器的时序要求发送给DDR2存储控制器,之后再接收DDR2存储控制器发回的读数据。DDR2存储控制器的读写操作时序如图3所示。

3 仿真验证

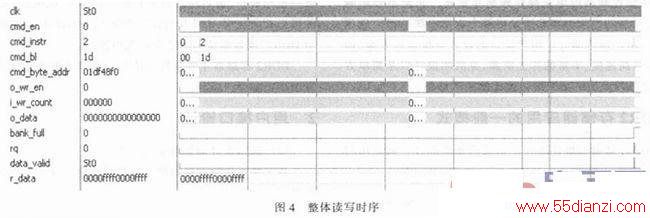

对本设计的验证采用的是6路8位数据以27 MHz的频率写入读出操作。对其进行整体读写仿真的时序结果如图4所示。

由该图可知,当将数据写入到DDR2中的数量到达一定程度时,开始向向外读出数据,写入的时序和读出的时序整体上符合设计要求。

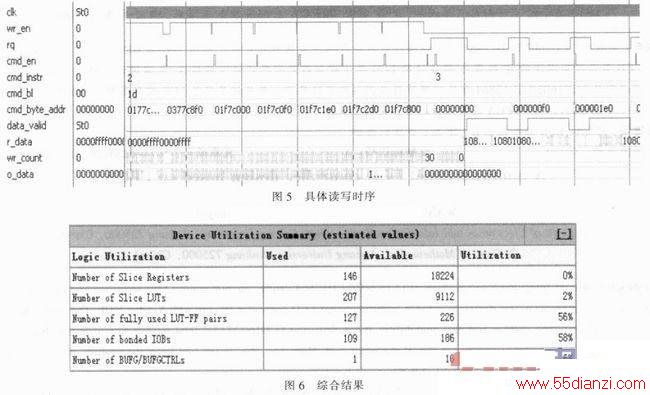

对读写操作的具体仿真时序如图5所示。

由该图可知,写操作时的各种控制指令以及地址和数据的发送都是完全正确的;读操作时的各种控制指令以及地址和数据的发送也是完全正确的。

对该设计采用XILINX Spartan6系列的xc6slx16—2ftg256器件进行综合,其结果如图6所示。

由该图可知该设计使用的逻辑资源相当小,其中寄存器还不到总数的百分之一,查找表也只使用了总数的百分之二。

4 改进

在一般情况下,DDR2的硬件存储速率很快,其会等待存储控制器发送下一个操作指令,而DDR2存储控制器的操作指令是由用户接口发出的,因此可以提出以下改进方案。可以在存储控制器前端添加多个FIFO,将与操作有关的所有指令、地址以及数据对应起来存入这些FIFO中,这样等到DDR2存储控制器将本次操作完成之后自动将所有FIFO中与下次操作有关的指令和数据读出,直接进行下一次DDR2的操作,与此同时用户接口部分在这些FIFO没满的情况下,还仍然向这些FIFO中写入要操作的所有指令和数据。

5 结论

由以上仿真结果可知,该设计在整个设计读写频率很高时仍然可以保证所有数据的正确操作,不会存在数据的丢失或者错误。由以上综合结果可知,该设计占用的FPGA片上资源很少,运行频率很高,基本可以满足所有设计的要求。因此可知,该设计具有很高的工作频率,解决了电路设计中DDR2存储器读写操作频率的瓶颈问题,使得整个设计的工作效率得到很大的提高。

上一篇:火控计算机接口电路的设计