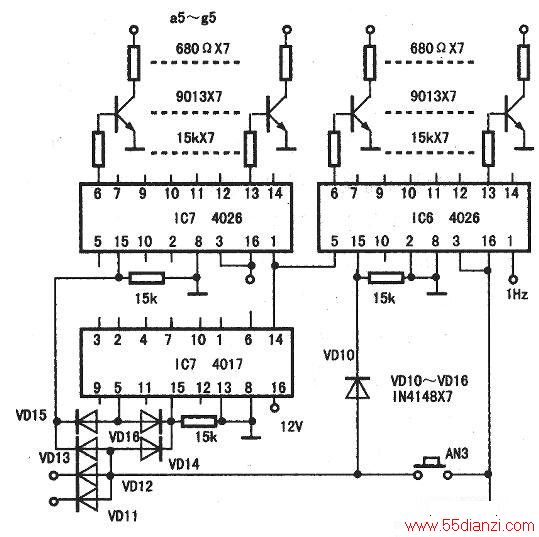

上图为LED数字钟60秒显示驱动电原理图。由于数字钟电路LM8363不能直接输出60秒信息,因此这里设计了由IC6、IC7、IC8构成的60秒显示驱动电路。其中IC6、IC7为两片CD4026(十进制计数—七段译码器),CD4026的1脚为时钟脉冲输入端,6、7、9、10、11、12、13脚为七段数码输出端,经三极管反向后驱动60秒显示两位共阳极双色七段数码管(用于“时,分”显示的3位半双色数码则由图3所示的电路来驱动),15脚为复位端。IC8为CD4017(十进制计数一时序译码器)。AN3为数字钟芯片IC1(LM8363)分钟设置按钮,当AN3揿下时,12V电压通过二极管VD11至LM8363的分钟设置端34脚,使数字钟处于分钟校正状态,同时二极管VD10、VD12、VD13、VD14均处于正偏,使IC6(CD4026)、IC7(CD4026)、IC8CD4017同时复位,此时两位60秒数码管显示“00”,而十进制计数——时序译码器IC3(CD4017)的第1路输出端3脚则为高电平。当分钟设置完毕松开AN3的瞬间,分钟和秒的计数同时开始,这样就做到了秒和分钟的进位保持同步。

随着十进制计数—七段译码器IC6(CD4026)1脚的1Hz秒闪脉冲(来自数字钟电路LM8365第40脚)的输入,其输出端的七段数码由O→1→2→3→4→5→6→7→8→9的变化,当七段数码由9回到0时,IC6(CD4026)的5脚输出第1个进位脉冲至十进制计数—七段译码器IC7(CD4026)的1脚,使其输出端七段数码由0变为1,同时十进制计数一时序译码器IC8(CD4017)的第2路输出端2脚为高电乎。当IC6(CD4026)的5脚依次输出第2、3、4、5个进位脉冲时,IC7(CD4026)输出端的七段数码显示依次为2、3、4、5,而十进制计数一时序译码器IC8(CD4017)的4、7、10、l脚依次输出高电平,当十进制计数—七段译码器IC6(CD4026)的1脚输入第60个秒闪脉冲时,其5脚输出第6个进位脉冲,使十进制计数一时序译码器IC8(CD4017)的5脚为高电平,此高电平使IC7(CD4026),IC8(CD4017)、同时复位,此时60秒显示的两位七段数码为“00”,至此IC6、IC7、IC8完成了60秒的显示过程。当十进制计数一七段译码器IC6(CD4026)的1脚继续输入1Hz秒闪脉冲,重新开始60秒的显示。这里VD11~VD16组成二极管逻辑,实现“与”,“或”功能。

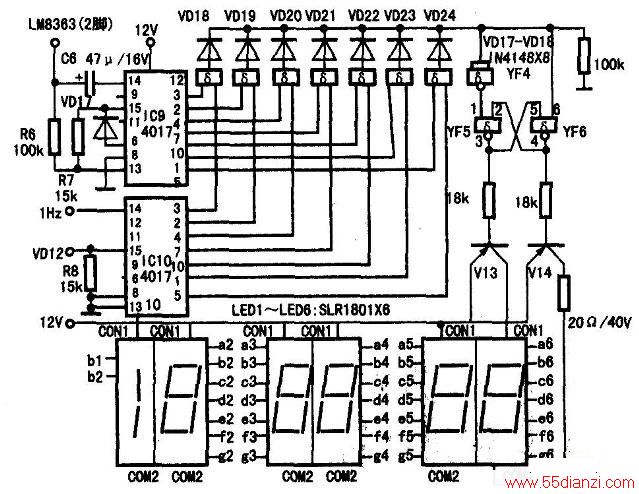

下图为数字钟星期信息生成电路,其中IC9(CD4017)和IC10(CD4017)为两片十进制计数一时序译码器,IC9、R6、R7、C6、VD8构成星期脉冲计数电路,星期脉冲取自数字钟集成电路LM8365第2脚(AM输出端),每天夜里12:OOAM端由低电平变为高电平,将此电平跳变经C6送至星期脉冲计数器IC9(CD4017)的14脚作为计数脉冲,因为每个星期七天为一个循环周期,因此将十进制计数一时序译码器IC9(CD4017)的第8路输出端6脚经二极管VD17至其15脚(复位端),同样道理,当十进制计数一时序译码器IC9(CD4017)的14脚每输入1个星期计数脉冲,其7路输出端依次输出高电平,任意时刻只有1路输出高电平,其它6路均为低电平,IC10(CD4017)作为秒脉冲计数电路与IC6(CD4026)同时复位,同步计数。

上图中的与门YO~Y6为两片CD4081(2输入端四与门)作为星期信息比较电路,VD18~VD24为隔离二极管,由YF4、YF5、YF6(CD4011:2输入端四与非门)构成施密特触发器,三极管VT3和VT4分别受控于施密特触发器中的YF5、YF6的输出端,由此可知三极管VT3和VT4输出状态互为相反,VT3截止→VT4导通→COM2=12V→个位秒显示数码管为绿色;VT4截止→VT3导通→COMl=12v-价位秒显示数码管为红色。

因为每个与门的两个输入端由相应的星期信息和秒信息构成,根据逻辑电路“相与“即相乘”的原理,只有相应的与门两个输入端均为高电平时,其输出端才为高电平,此时施密特触发器中YF4输出低电平,YF5输出高电平(VT3截止),YF6输出低电平VT4导通),60秒显示的个位双色七段数码管为绿色,此时的秒信息也是星期信息(显示时长1秒),而前4位双色半七段数码管始终保持红色。

当与门YO输出高电平,即60秒显示的两位七段数码为00,10,20,30,40,50时,其个位双色七段数码管由红色变为绿色,表示为星期日;与门Yl输出端为高电平时,60秒显示的两位七段数码为01,21,31,41,51时,其个位双色七段数码管由红色变为绿色,表示为星期一…当与门Y6输出端为高电平,即60秒显示的两位七段数码为06、16、26、36、46、56时其个位双色七段数码管由红色变为绿色,表示为星期六,这样在60秒显示的个位双色七段数码管上每10秒叠加1秒的星期信息,由3位半“时:分:”驱动电路、60秒显示电路及数字钟星期信息生成电路组合在一起,从而实现了在5位半双色数码管上的“时:分:秒”时间信息以及星期信息的完整显示。

本文关键字:暂无联系方式时钟-定时电路,单元电路 - 时钟-定时电路

上一篇:智能音乐打铃电路