Omapdce.ko模块将作为一个RPMsg driver,其实现了应用程序引擎相关API的内核实现,主要包括ioctl_engine_open()、ioctl_viddec_create(),ioctl_viddec_control()、ioctl_viddec_process(),他们提供了应用API engine_open、viddec_create()、viddec_control()、viddec_process()的驱动实现,这些驱动函数将调用RPMsg总线rpmsg_send()、rpmsg_recv()与协处理器进行消息通信以完成工作任务。

3.1.4 解码应用viddectest实现

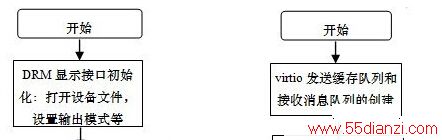

H264解码应用程序viddectest的工作主要分为以下几个方面

1)Linux显示接口DRM初始化,通过Drmopen()函数打开/dev/dri/card0设备文件,获取设备资源drmModeGetResources(),创建帧缓存drmModeAddFB2()及设置输出分辨率及模式drmModeSetCrtc()

2)FFMpeg媒体库的调用,通过AVOpenStreamFile()打开多媒体文件,AVFindStream()分离出音频流和视流,然后依次通过AVGetPACket()读取视频流数据包送去解码器进行解码。

3)加速引擎初始化和利用消息总线进行解码数据通信,通过Engine_open()打开H264解码引擎,Viddec3_create()创建一个解码实例对象,Viddec3_control()设置解码所需的参数,Viddec3_process()将用RPMsg消息总线送出解码数据流并接收解码后的图像缓存数据,其流程图如图5所示:

3.2 Cortex-M3软件实现

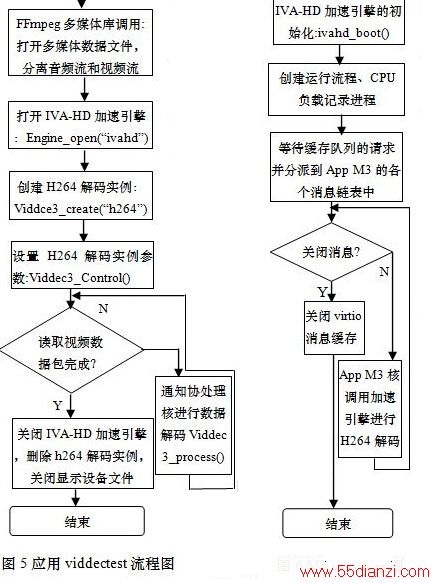

双核Cortex-M3运行TI BIOS实时操作系统,负责与主处理核的virtio缓存队列通信及通过CODEC engine调用IVA-HD加速引擎实现H264解码,运行流程图如图6所示,主要包括以下内容:

1) virqueue_create(&send_queue),virqueue_create(&recv_queue)创建与Cortex-A9主处理核通信的 virtio发送及接收缓存队列。

2) Message_get_queue(&recv_queue)从virtio缓存队列获取主处理核发过来的请求数据,Message_send_queue派发到App M3的消息队列中。

3) App M3将获取消息链表的消息,设置IVA-HD加速引擎的工作状态并初始化,如果为解码消息则通过Codec Engine 调用IVA-HD加速引擎来完成解码过程。

4) 将解码后的图像缓存封装成virtio缓存,调用Message_send_queue()通过virtio缓存队列发送回主处理核A9调用DRM进行显示输出。

4 测试

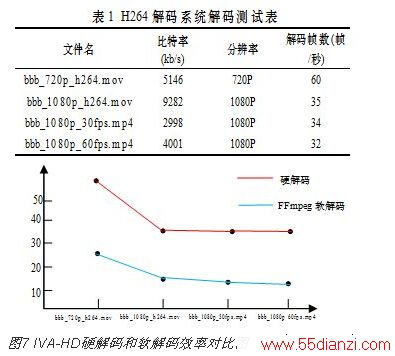

本文在OMAP4430开发平台上设计实现了基于异构多核的全高清H264解码,为了测试解码器的性能,将针对不同比特率的720P、1080P 的网络视频文件Big_Buck _Bunny_Sunflower 进行解码测试,测试结果如表1所示,同时采用FFmpeg开源库项目的软解码进行测试,其对比图如图7所示

图7 IVA-HD硬解码和软解码效率对比图

从图6可以看出本次设计的H264解码器在解码720P(1280*720)和1080P(1920*1080)视频时分别达到60和34帧每秒,相比FFmpeg开源H264软解码器效率提高了一倍。而普遍全高清流畅视频的帧率为30帧每秒,达到实时解码性能需求。

5 结束语

随着移动互联网时代的到来,在移动终端上流畅播放全高清视频成为任务日常需求。为此本文采用移动Soc OMAP4430异构多核处理器为实验平台,通过基于virtio缓存队列和RPMsg消息框实现了异构多核间多媒体数据通信,同时结合IVA-HD多媒体硬件加速引擎设计了一款全高清H264视频硬解码系统。实验结果表明设计的解码系统比开源FFmpeg软解码器在性能上提升了一倍,达到实时性要求。具有解码速度快、解码过程由硬件加速器完成无需消耗主核运算资源、核间通信效率高、功耗小等优点。

本文关键字:暂无联系方式编、解码-加、解密电路,单元电路 - 编、解码-加、解密电路

上一篇:无线遥控编译码电路工作原理