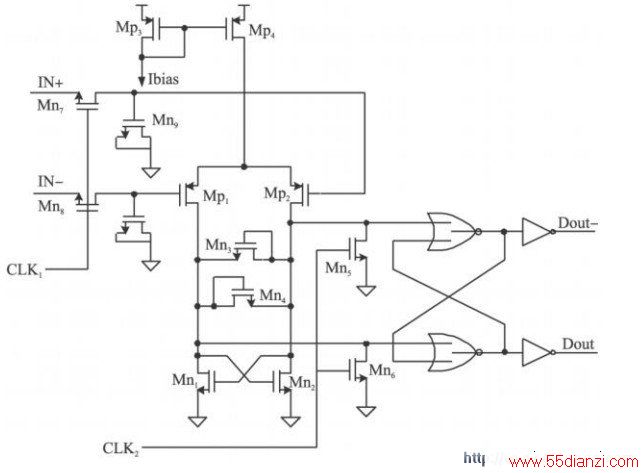

图6 1 bit量化器

4. 3 开关电容DAC

开关电容DAC由MOS开关,电容和电阻组成,如图7所示。在第一个时钟相,开关S1 闭合, S2 断开,上下电容两端的电压为±0. 5Vref。在第二个时钟相,开关S2 闭合, S1 断开,电容放电,开关D 和DN决定放电通路。为了减小电荷注入效应,开关S1 比S1d提前闭合。输出端接第一级运放的输入,所以在第一个时钟相开关电容DAC的输出端电压等于运放的输入共模电压VCM 。

图7 开关电容DAC

5 仿真结果

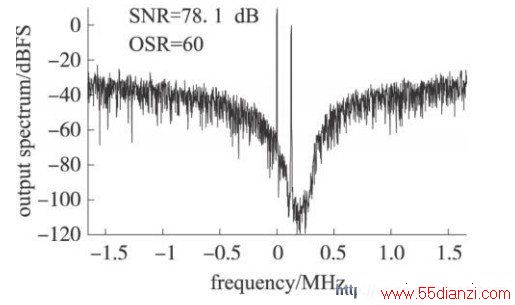

四阶连续时间正交带通ΣΔ调制器采用smIC0. 13 mixed2signal CMOS工艺实现。采样频率为12MHz,过采样率为60,有效带宽为200 kHz,中心频率为200 kHz。用SpeCTRe进行仿真验证,当I、Q两路的输入分别为125 kHz的正弦和余弦信号时,调制器的输出功率谱密度如图8所示,整个频谱近似关于f = 200 kHz对称,其SNDR为78 dB。

图8 输出频谱密度

6 结论

本文提出了一个基于复数滤波器的四阶连续时间带通ΣΔ调制器电路,非常适用于低中频架构。

调制器采用开关电容DAC,有效减少了时钟抖动效应的影响。

本文关键字:暂无联系方式调制与解调电路,单元电路 - 调制与解调电路

上一篇:射频调制器的信号流程分析