module Mini51b_PWM(P0,ALE,P27,WR,PWM);

input [7:0]P0;

input ALE,P27,WR;

output [2:0]PWM;

wire [3:0]addr;

reg [7:0]daPWMc;

reg [7:0]daPWMs0,daPWMs1,daPWMs2;

reg [2:0]PWM;

wire clk,nclk,a,b,c,d;

assign addr= (ALE)?P0[3:0]:addr; // 低八位地址锁存

always @(negedge WR)

begin

case({P27,addr})

5'H10: daPWMs0 <= P0;// 写带地址的寄存器

5'H11: daPWMs1 <= P0;// 写带地址的寄存器

5'H12: daPWMs2 <= P0;// 写带地址的寄存器

default:

begin

daPWMs0 <= daPWMs0;

daPWMs1 <= daPWMs1;

daPWMs2 <= daPWMs2;

end

endcase

end

always @(posedge clk) begin

daPWMc <= daPWMc+1; //PWM 调整精度1%

if(daPWMs0 < daPWMc) PWM[0] <= 0;//PWM 发生器

else PWM[0] <= 1;

if(daPWMs1 < daPWMc) PWM[1] <= 0;//PWM 发生器

else PWM[1] <= 1;

if(daPWMs2 < daPWMc) PWM[2] <= 0;//PWM 发生器

else PWM[2] <= 1;

end

assign nclk=!clk;

LCELL A0(。in(nclk), .out(a));

LCELL A1(。in(a), .out(b));

LCELL A2(。in(b), .out(c));

LCELL A3(。in(c), .out(d));

LCELL A4(。in(d), .out(clk));//PWM 时钟来自CPLD 内部

LCELL 延迟电路振荡器

endmodule

与之对应的MCU 演示程序:

#include

#include

#define PWM0 XBYTE[0xfff0]

#define PWM1 XBYTE[0xfff1]

#define PWM2 XBYTE[0xfff2]

unsigned char code sine_dot[36]= //8 阶,36 点正弦表

{

0x80,0x96,0xab,0xbf,0xd2,0xe2,0xee,0xf8,0xfe,0xff,0xfe,0xf8,

0xee,0xe2,0xd2,0xc0,0xab,0x96,0x80,0x69,0x54,0x40,0x2

d,0x1e,

0x11,0x07,0x01,0x00,0x01,0x07,0x10,0x1d,0x2d,0x3f,0x53,

0x69

};

void main()

{

unsigned char a,b,c;

a=0;

while(1) {

a %= 36;// 对36 取余数及0~35

b=(a+12)%36;// 较a 路滞后120 度相位

c=(a+24)%36;// 较a 路滞后240 度相位

PWM0 = sine_dot[a];

PWM1 = sine_dot[b];

PWM2 = sine_dot[c];

a++;

}

}

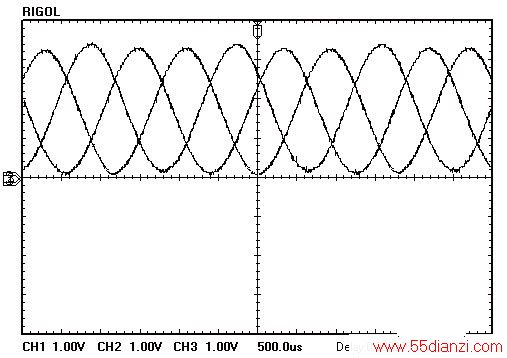

实际得到的三相正弦信号示波器截图效果如图7所示,只是双踪示波器同时只能看两路信号。

图7 具有精确相位差的三相正弦信号示波器截图

五、结束语

今后,MCU+CPLD 结构将是很多电子系统设计的一种基本架构,MCU 可以用程序实现复杂智能的控制与检测,CPLD 又可以实现灵活多变的外围扩展电路设计,尤其是可以用硬件实现特殊的MCU 无法实现的功能,弥补MCU 响应速度慢影响实时性问题,两者互补,完全实现硬件软设计,使得同一硬件平台能够通过软件实现更多的功能。