为了满足外场装备检测装置的便携化和信号采集的实时化要求,基于PC104总线的高效数据传输特点,采用了上位机控制板和信号采集板相结合的嵌入式系统搭建方法,在信号采集板中通过FPGA控制逻辑实现了多通道开关、信号调理电路和A/D转换器的配置,并把采集的信号数据传输给上位机控制板进行实时显示。应用结果表明,该实时信号采集处理系统操作简单,具有较高的实时性和稳定性。

PC104是嵌入式工控机的一种,其外部总线接口为PC104总线。使用堆叠的方式可以将多个PC104主板结合到一起,并通过螺栓固定,保证系统的牢固可靠,应对恶劣的使用环境。由于PC104具有功耗低,体积小,扩展性高,功能强大等优点,其已经在航空航天、军用武器装备、工业控制等领域得到了广泛的使用。

在对武器装备进行测试维护时,经常需要对设备中的各类模拟信号进行分析,从而对武器系统的运行情况做出判断。目前常见的测试设备往往实时性不高,无法更多地进行人机交互。同时由于测试设备体积过于庞大,并不方便在外场对武器装备进行直接的测试和维护。随着现阶段军用装备外场测试的信息化程度逐渐提高,迫切需要研制出体积小、结构紧凑的便携式实时测试设备。

目前主流的实时信号采集方式是通过高速A/D转换器件来完成的,其优点是信号精度高,实时的信号采集带来了大量的数据需要处理,对后端的信号处理系统提出了较高的要求。因此本文搭建了基于PC104总线的实时信号采集处理系统,凭借FPGA的高速处理能力控制A/D转换器完成数据的采集,并通过PC104总线将数据提供给上位机完成用户对实时信号的监测。

1 总体设计方案

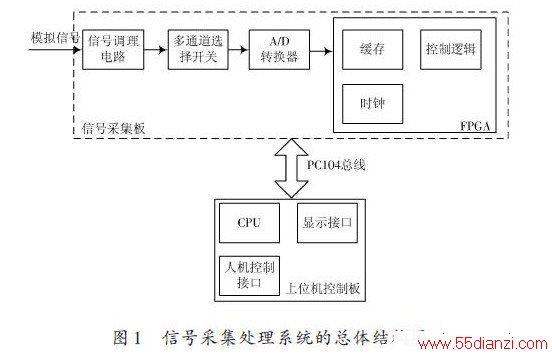

本文的实时信号采集处理系统主要包括信号采集板和上位机控制板2部分,两者之间通过PC104总线进行通信。上位机控制板以CPU为核心,扩展出VGA,RJ45等人机交互所需要的外围设备接口。信号采集板主要包括了FPGA逻辑控制、A/D转换器、通道选择开关、前端信号调理器等。实时信号采集处理系统的总体结构图如图1所示。

信号采集处理系统进行工作时,上位机控制板的CPU通过PC104总线向底层信号采集板发送命令,对其工作参数进行设置。CPU与FPGA之间通过地址和数据总线完成命令及数据的交互。多通道选择开关对外部输入的模拟信号进行通道选择,在信号调理芯片对模拟信号进行相应的预处理之后,在FPGA的逻辑控制下由A/D转换器完成信号的采集。FPGA通过PC104总线实时地将采集的信号数据传输给CPU,通过运行在上位机控制板的应用程序完成数据的最终分析和处理。信号采集处理系统可以通过FPGA逻辑控制模块灵活地调整采样速率,来满足多种信号不同速率的采样要求。

2 硬件系统设计

2.1 上位机控制板

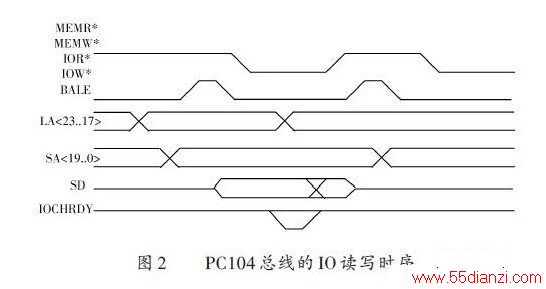

本系统采用深圳盛博公司的PC104模块SCM9022作为上位机控制系统硬件平台,其处理器为英特尔凌动N455处理器,使用了1 GB的DDR3内存,支持2 GB的SSD和1路SATA接口,支持2个100 Base-T以太网口,具有8路GPIO接口和6个串口,4个USB 2.0接口,标准鼠标键盘接口,支持18位的LVDS和VGA显示。SCM9022的硬件资源可以满足对所需要采集信号的处理,用户可以方便地使用其通用的外设接口完成必要的人机交互。上位机控制板包括了64针脚的双排单列插针J1和40针脚的双排单列插针J2,总共104根信号总线。上位机控制板是标准的PC104模块,其尺寸为96 mmx90 mm。当工作在8 b数据模式下时,J2的针脚信号无效,只有J1针脚有效;当工作在16 b数据模式下时,J1和J2所有针脚都有效。在104个针脚中,包括了16个数据针脚,7个锁存地址针脚,20个地址针脚,32个控制针脚,14个地线和电源线,1个14 MHz的OSC,1个8 MHz的BCLK。其中,SA[0..11]为地址总线;SD[0..7]为数据总线;IOR为输入/输出接口的读控制,低电平有效;IOW为输入/输出接口的写控制,低电平有效;DATA为串行数据;BALE为地址锁存信号;CLK为移位脉冲;SY-CLK为总线时钟;IOCHADY为输入/输出接口的准备就绪信号,该信号由集电极开路门或三态门驱动,低电平时处于无效状态,表示输入/输出接口设备需要将总线的周期延长。时序如图2所示。

2.2 信号采集板

为了能快速高效保证上位机控制板与信号采集板之间的PC104总线数据通信,底层的信号采集板使用了ALTEra公司的CycloneⅢ系列FPGA芯片EP3C25F256C7N,通过控制逻辑来按照PC104总线的时序进行数据传输。该芯片具有200 Kb逻辑单元、8 Mb嵌入式存储器以及396个嵌入式乘法器能够在控制信号采集芯片的同时,将采集的信号数据传输给上位机。需要注意的是,由于PC 104总线的针脚都是5 V电平,而FPGA芯片采用了3.3 V的电平信号,所以在信号采集板上使用了74LVH162245芯片对电平进行转换,调整电气特性,完成由TTL电平向LVTTL电平的转换,并增强驱动能力。在信号的采集过程中,由于外部的多路模拟输入信号往往比较微弱,其电平的幅度很小,为了保证A/D转换模块采集到足够强的信号幅度,在信号采集板中使用了放大器INA103把输入信号进行调理放大到0~10 V之间。INA103是由BB公司生产的低功率增益可调通用仪器放大器,其具有高精度宽带宽的特点。在增益为100时,对应的带宽仍达到200 kHz。该芯片采用了可调电阻调整放大倍数,具体公式如式(1)所示:

G=1+6 kΩ/R (1)

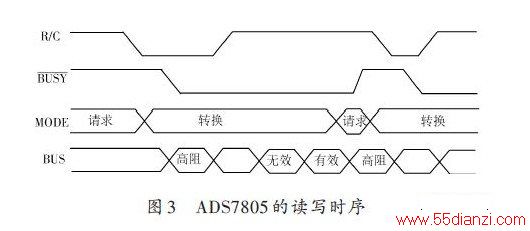

本系统在信号采集板中采用了R=6 Ω,故得到的放大倍数在0~1001之间,保证了该芯片输出给A/D转换器的信号电平在0~10 V之间。信号采集板的多路选择开关采用了AD公司的ADG508A八选一高速选通开关。系统通过2片ADG508A并行控制模拟信号的输入,实现了对16路信号的实时采集。多路开关的输入通断是通过控制使能引脚EN以及CH0,CH1,CH2来完成的,FPGA输出的地址的最高位分别接到2片ADG508A的使能端,地址低3位分别接入ADG508A的AO,A1,A2。信号采集板的A/D转换芯片采用了BB公司的ADS7805,其具有高速、低功耗的特点。在5 V的工作电压下其最高的转换频率达到了100 kHz。该芯片内部自带有时钟、电压基准和采样保持等电路,极大的简化了用户的电路设计,并且提高了系统的稳定性。ADS7805采用了逐次逼近式工作原理,A/D转换结果通过16位数据总线并行输出,输入的模拟信号电平范围为0~10 V,其工作时序图如图3所示。

3 软件系统设计

实时信号采集处理系统的软件部分包括了信号采集板的FPGA控制逻辑和上位机控制板运行的应用程序。信号采集板在FPGA控制逻辑下实现了信号的采集和传输,上位机控制板通过应用程序完成人机界面的交互和数据控制处理。

3.1 FPGA控制逻辑的设计

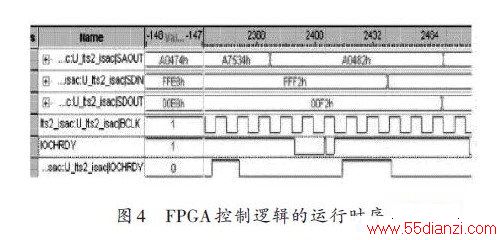

FPGA控制逻辑是整个数据采集过程的核心部分,它所实现的功能包括:对多路选通开关ADG508A的控制,对地址总线进行译码,对A/D转换模块ADS7805的控制,将采集的数据在FIFO中进行存储等。FPGA控制逻辑工作时的操作时序如图4所示,其在一个总线操作周期内的工作流程按如下顺序进行:

(1)FPGA上电后,首先进行全局复位,数据总线设置为三态,地址锁存清零。

(2)等待BALE信号进入下降沿的有效状态,对PC104的地址总线进行锁存。

(3)等待IOR/W信号有效,对地址进行解码,将锁存的地址信息译码。

(4)对地址进行比对,若比对正确则准备就绪,若比对不正确则将地址锁存器清零,数据总线设置为三态。

(5)等待PC104数据周期有效时,接收上位机控制板传输过来的动作命令数据。

(6)控制INA103芯片对输入的模拟信号进行调理。

(7)控制ADG508A芯片进行通道选择。

(8)控制AD7805芯片开始进行数据采集。

(9)以输入输出端口的OE信号为触发脉冲,对所采集的信号数据进行锁存控制。

(10)等待OE信号拉低,采集数据的锁存结束,将数据通过总线传输给上位机控制板。

(11)等待数据传输周期结束,将地址锁存清零,数据总线设置为三态。

(12)等待下一个时钟周期到来,再次重复进行读写操作。

3.2 应用程序的设计

上位机控制板运行的应用程序主要完成用户对信号采集板的控制和监视,将所采集到的信号实时在显示器上进行更新显示。由于整个系统在外场进行使用时的环境条件往往比较恶劣,且经常会遇到断电的情况,因此在上位机控制板运行了Windows

本文关键字:暂无联系方式传感-检测-采集技术,电子知识资料 - 传感-检测-采集技术