FPGA在单片机输出使能信号EN和数据类型信号Dsel控制下,输出所测信号的频率和相位差所对应的二进制数据仿真波形如图5所示。VHDL程序经过编译调试生成.pof文件下载到配置芯片EPCS1中实现所设计的功能。

4.2 ATmega128运算控制程序设计

AVR单片机ATmega128从FPGA分别读取频率和相位差的20位数字量,由于FPGA在20 MHz数据采集信号作用下对待测信号周期和两同频信号的相位差所对应的时间差计数,因此20位数字量的单位是0.05μs,单片机对这些数字量进行计算,可以得到待测信号的频率和相位差。

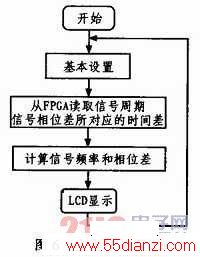

单片机运算控制程序设计思路:单片机(ATmega128)通过控制信号EN和Dsel从FPGA(EP1C3T100)读取待测信号的周期和两待测信号相位差所对应的时间差,对读取的数据进行计算、转换,送液晶显示器显示,显示待测信号的频率、相位差以及有关信息。主程序流程图如图6所示。源程序由主程序及若干子程序组成,主程序是一个循环执行程序。

1)单片机从FPGA读数据

根据MCU与FPGA的20位数字量的接口,从单片机的PA、PB和PC(低4位)读取数据,组合成20位的数据,控制线EN和Dsel控制FPGA释放数据。当Dad=1时,FPGA向单片机传送待测信号的相位差数据;当Dsel=0时,FPGA向单片机传送待测信号的周期数据;当EN=1时,FPGA向单片机释放数据,当EN=0时,FPGA禁止向单片机释放数据。

2)频率和相位差数据的运算

为了测量达到要求的精度,在运算时不能丢失数据,所以采用扩大倍数定点取数的方法,保证数据计算准确。依据如下方法进行计算:信号频率F=106/T,计算结果精确到1 Hz;相位差△θ=△tx360°x10/T,计算结果精确到0.1°。

3)LCD显示器显示频率、相位差等相关信息

本设计采用HTM12864(128x64)的LCD液晶显示器,控制器为S6B0724,与单片机数据与控制接口是:CS、RET、D/C、SCLK、DATA,背光灯根据按键动作控制,用按键来切换显来示信息。

5 结论

本设计采用MCU和FPGA相结合的方法,ATmega128单片机具有先进的RISC结构和运算控制功能,而FPGA集成度高、高频率的数据采集功能强劲,它们发挥各自的优势。均具备JTAG接口在线调试和编程功能,用此方法设计的数字式相位测量仪具有较高的精度,稳定可靠。本仪器测量正弦信号的频率及两个同频正弦信号的相位差,较好地满足了设计的技术指标要求。