1、分数N PLL PLL的操作由32位配置寄存器控制。利用15位数值的频率来决定RF载频,RF载频软件编程允许IC的某些多通道应用。所选择的调制类型带1位的ASK-NFSK标志,FSK调制通过在反馈环路中修改除法器实现。8位数值的FSEP完成FSK频率偏移,这种频偏以每步±396Hz从±396Hz到±lOlkHz。PLL带宽为140~380kHz(典型值为280kHz),PLL的时钟时间在利用13.0000MHz晶体时为98.46ms。

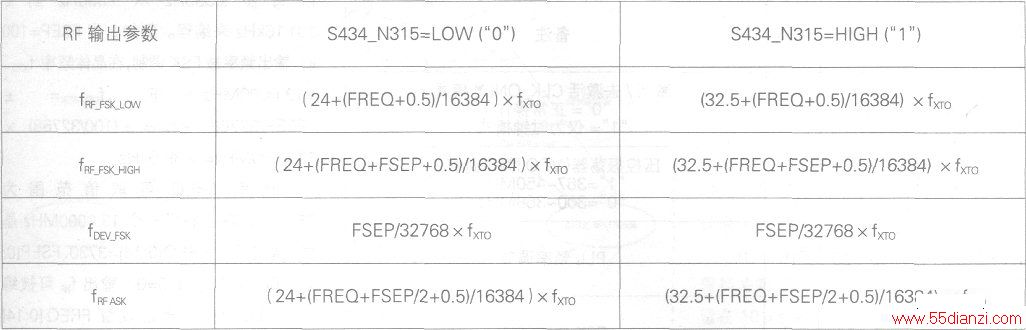

2、RF载频选择 分数除法器可按照上表所示的公式编程来产生一个RF输出频率fRF。对于fRFASK,如果FSEP是一个奇数,FSEP/2值应下舍到下一个整数值。FSEP可取值为1~255。当使用13.OOOOMHz晶体时,频偏fDEV_FSK范围可以每步±396Hz从±396Hz到±101.16kHz来编程。例如,当FSEP=100时,输出频率被FSK调制,在晶体频率fxro=13.OOOOMHz下,fDEV_FSK=±(FSEP/32768)×fXTO=±(100/32768)×13.OOOOMHz=±39.6kHz。

频率FREQ可取值范围为2500~22000.利用一个13.OOOOMHz晶体,通过设置FREQ[0:14J=3730、FSEP[O:7]=100、S434_N315=0,输出fRF可被编程到315MHz;通过设置FREQ[0:14]=14342、FSEP[0:7]=100、S434_N315=1,fRF可实现433.92MHz。

3、功率放大器 ATA5749的PA是一个带开路集电极输出交付电流脉冲的C类放大器。当PLL锁定并且配置寄存器编程完成时,PA使能。在FSK模式上PA使能,RF输出功率开通。在ASK模式,输入信号必须为输出脚上的RF设置到高电平。PA的输出功率可以每步约ldBm进行编程,范围为-0.5dBm~+12.5dBm。PA输出电流脉冲峰值lpulse在上电复位(PWR)时可用4-bit值编程,从而使用户可将输出功率和电流消耗标度到最佳电平。

4、晶体振荡器 ATA5749的晶体振荡器是一种有固定功能的振幅调节精密振荡器,它在EN置位时使能。在振荡器输出幅度达到可接受的电平后,XTO_RDY被置位。如果CLK_ON置位,引脚CLK则变为有源,PLL接收它的参考频率。当使用一个小尺寸晶体(如3.2mm×2.5mm)并带4fF的动态电容CM时,晶体振荡器的启动时间约为200μs。5、时钟驱动器时钟驱动器利用配置寄存器中的CLK_ONLY、CLK_ON和DIV_CNTRL位进行编程。当CLK_ONLY被清除时,正常操作被选择。当CLK_ONLY被置位时,CLK输出使能。当DIV_CNTRL被置位时,时钟除法器可被设置到除以4;当DIV_CNTRL被清除时,则可设置到除以8。当利用一个13.OOOOMHz的晶体时,将产生3.25MHz或1.625MHz的输出。当CLK_ON被清除时,在CLK脚上没有时钟可利用,发射器有一个较小的电流消耗。CLK信号用于为微控制器计时,它在1.625MHz和3.25MHz上可分别驱动直达20pF和lOpF的负载电容。在IC关闭状态和上电时,CLK输出低电平。当晶体振荡器幅度检测器检测到足够的幅度和XTO_RDY与CLK_ON被置位后,CLK输出变为有源。

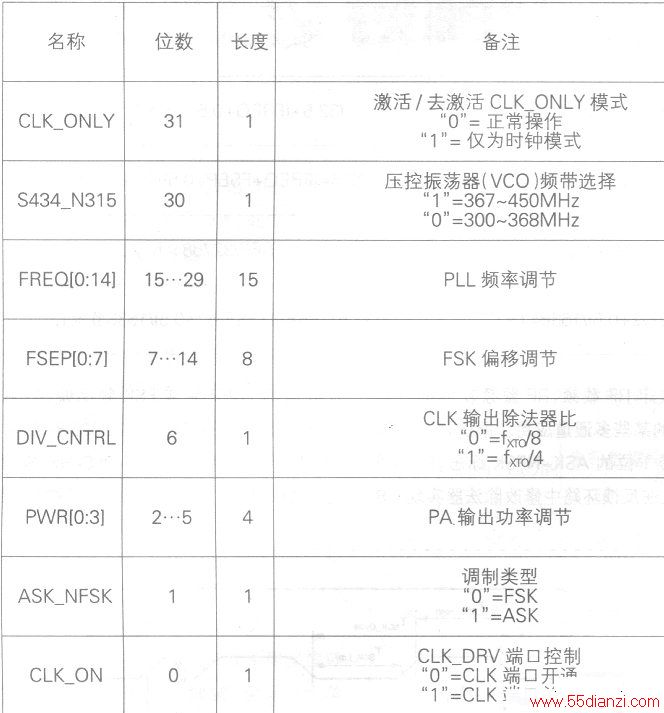

6、配置寄存器及其编程在上电或当改变PLL发送器的工作参数时,用户必须编程配置寄存器的所有32位。下表列出了控制寄存器的位赋值。

控制寄存器的功能如下表所示。

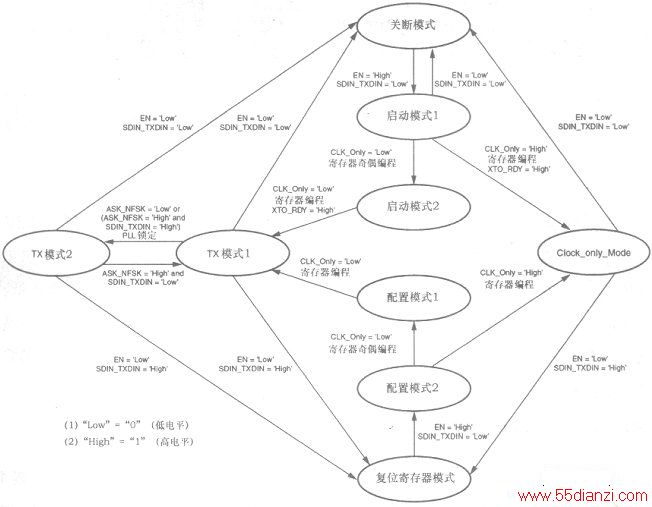

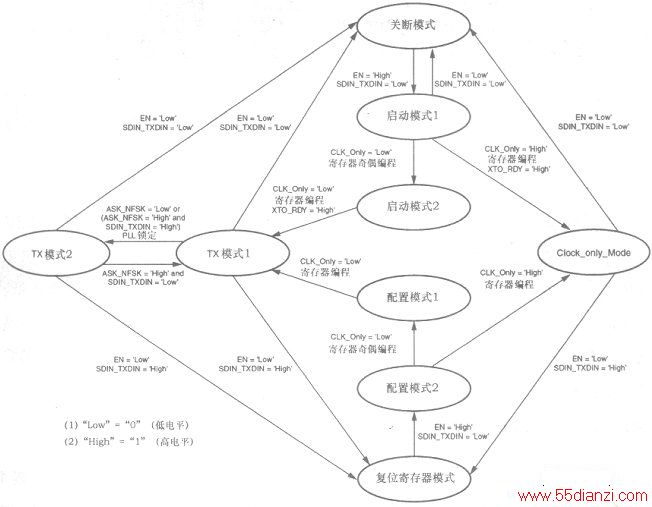

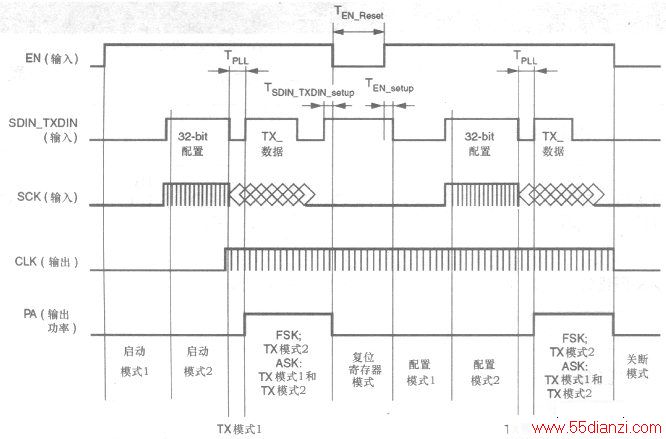

配置寄存器利用SPI总线从MSB开始编程,它由使能线(EN)、数据线(SDIN_TXDIN)和SPI总线时钟(SCK)组成。SDIN_TXDIN数据在SCK正沿上加载,配置寄存器的内容在编程顺序的末位(LSB)的负SCK沿上变成程序。下图为SPI总线的定时图。在32位程序设计顺序结束时,SDIN_TXDIN线为RF发送器编程调制输入。在编程完成后,SCK信号对器件没有作用。为使发送器截止进入关断模式,EN和SDIN_TXDIN必须回复到低电平状态。

在配置寄存器被编程和RF数据发送完成之后,器件将进入关断模式,晶体振荡器和PLL则停止操作。在未进入关断模式,欲修改配置寄存器内容,可以使用复位寄存器模式。为进入复位寄存器模式,在至少lOμs的复位最短时间内,当EN为低电平时,SDIN_TXDIN必须维持在高电平。

在复位寄存器模式,PA和分数PLL保持关断,但XTO则保持有源,该状态停留在lOμs的时间上,紧接着需要首先升高EN和带lOμs延迟的SDIN_TXDIN。在该模式下,32位配置寄存器数据被发送到SPI总线上。在数据发送之后,器件被转换回关断模式。其间,EN、SCK和SDIN_TXDIN必须维持在低电平。下图显示出了利用复位寄存器模式时编程定时图实例。

下图所示为ATA5749的工作模式状态图。事实上,ATA5749工作模式是有源电路的函数,如下表所示。