存储集成电路,常称存储器,俗称记忆块。根据工作原理分类可以分为随机存储器RAM与只读存储器ROM等。其中RAM是一种随机读写存储器(RandomACCessMemory),能够随时在任一地址读出内容或写入新内容。RAM的主要优点是:使用灵活、读写方便;突出缺点是:不能长期保存信息,一旦停电,所存信息就会丢失。它分为静态RAM(SRAM)、动态RAM(DRLAM)。

ROM是—种只读存储器(Read-OnlyMemory),它可以分为ROM、RROM、EPROM(可擦式可编程只读存储器)、E2PROM、FlashMemory(闪速存储器)等,此类存储器中内容一经写入,在工作过程中就只能读出不能重写,即使掉电,写入的内容也不会丢失。

显示器中一般除了微处理集成电路等集成电路内置了存储器外,还专门采用了存储集成电路,目前,主要是与微处理集成电路配合使用的电可擦可编程存储器,即EEPROM或者E2PROM。

EEPROM具有在线可读可改写以及掉电能保存数据等特点,它基本上集成了RAM与ROM的优点。

EEPROM集成电路有并行接口型与串联接口型。其中,并行接口型优点是速度快、容量大等,缺点是价格高、功耗大等。串联接口型优点是体积小、功耗小等,缺点是读写繁、速度慢等。另外,对于串联接口型EEPROM有一个特点是:所有DIP封装结构的产品,均为共8引脚(即DIP-8结构,实物如上图、下图2示),而且引脚输出兼容。

EEPROM在显示器中数据丢失的情况较少,但是因干扰脉冲、噪声尖峰等原因有时也可能丢失数据。

EEPROM-般厂家设计具有软件保护数据或硬件保护数据的特性。其中,硬件保护数据有几种方法,其一是EEPROM内部设计了电源电平检测电路,当电源电压低于一定数值,则不能够写入数据:其二是三线写入控制,即/OE输出允许端、/CE片选端与/WE写允许端中三线当任何一根线处于无效写电平,则EEPROM均不可写入数据,一般EEPROM是要求/OE输出允许端为高电平(即H),/CE片选端与/WE写允许端同时均为低电平(即L)。另外,还有一些方法是上电延时、利用噪声滤波器等均可达到保护数据丢失的目的。

在多频数控显示器中,一般存储器与微处理器均是通过IIC总线实现的。其中,EEPROM总线可以分为三总线制与二总线制。其中,三总线制主要由DI数据输入端、DO数据输出端与CLK时钟端;二总线制主要由SDA数据线与SCL时钟线,并且XX24CXX、XX24LCXXX。

XX85XXX等系列往往是二总线制,XX93CXXX、XX93LCXX等往往是三总线制。显示器广泛采用二总线制EEPROM。

二总线制EEPROM中的SDA引脚一般需要外接上拉电阻与电源相连,上拉电阻的阻值有采用5.1kΩ、4.7kΩ的,而且再与相连的电源电压的数值一般是+5V。其信号触发方式一般不是边沿触发,而是电平触发。此脚为双向输入/输出,为漏极开路结构,可以与外接开集电极或者开漏极外接件组合成线或关系的连接。其SCL端的脉冲与SDA需要对应好:一般写入数据时与SCL端上升沿同步;输出数据时与SCL下降沿同步,这样才能达到要求。一般通过万用表不便于检测,用示波器可以直观检测发现问题。

二总线制EEPROM,除了SDA、SCL引脚外,cs端与A地址选择端一般均具有,特别是CS端,无论是二总线制EEPROM还是三总线制EEPROM均有。对于显示广泛采用的共8引脚集成电路的A端来说,主要是因为控制字节的第1~4位按IIC总线规则已经定为1010作为片选识别集成电路的作用,而剩下的第5~7位供存储块、页面地址选择或者片选之用。因此分别标志为Al、A2、A3,引脚功能定为地址选择端。

除了以上引脚外,还有电源引脚与写保护端。其中,电源端常接+5V。

存储器一般采用CMOS化,因此诸多存储器具有CMOS集成电路的极低静态功耗,高集成度等优点外,同时也具有CMOS集成电路进行检修时需要注意的事项与其缺点:

(1)超大规模的CMOS集成电路内部单位元件内电路密度、电场强度等比分立件大很多,其除了开路、短路,电参数漂移外,还有漏电等故障。

(2)CMOS器件栅极容易击穿。

(3)CMOS电路的闩锁效应、芯片断裂,欧姆接触退化,引线断裂,腐蚀也是故障原因。

(4)检修CMOS集成电路时,要防止电源浪涌、静电放电、电压瞬变、工艺等原因。

(5)CMOS集成电路容易受电磁干扰影响,因此,可以通过输入端并接lMΩ电阻降低其输入阻抗,输入端与输出端各加接地积分电容器50~200pF,电源进线安装滤波器等。

(6)CMOS在一定场合受温度影响,因此注意其使用环境温度。

(7)高速CMOS集成电路HC与HCV为2~6V,HCT为4.5~5.5V。且一般用于5v电路电压,如果高于此电压需要用稳定的相应数值的稳压电路供电。

(8)当因电源有噪声时,可采用相应容量去耦。

(9)电源电压有的有正负之分,不能够接反。VDD、VCC一般接正极,Vss一般接负极。

(10)输入端的信号电压一般在Vss~VDD之间,超过此范围可以串联限流电阻10~100kΩ。多余的输入端不能够悬空,应按要求接VDD或者接地。工作速度不高时,可以允许与输入端并联使用。

(11)输出端不允许接VDD或者地。除了三态输出外,不允许两个器件的输出端连接使用。

(12)当测试时,应首先加电源,再加信号。关机时,首先去掉信号电源,再关电源电源。

(13)输入阻抗高,容易受外界干扰或者静态击穿,一般放在导电容器中。焊接时,电烙铁注意接地良好,以免击穿集成电路。

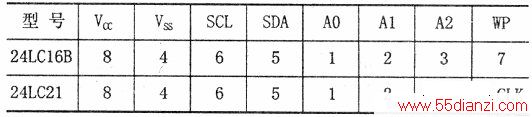

其中,MOS集成电路中的CMOS集成电路的闩锁效应要注意。CMOS电路的闩锁效应,在CMOS集成电路,在同一衬底上制作PMOS管与NMOS管,不可避免出现NPNP寄生可控硅结构效应。由于此效应存在,使得集成电路接通后,撤离触发信号,大的电源电流不会消失,从而在没有相应限流措施情况下,会引起电源端与接地端之间相连的金属化层或者相关引线断开,在输入/输出电压超过或者低于相应电压或者电源电压超过元器件额定工作电压很多时,击穿一般会发生。目前,MOS集成电路一般均有防此效应电路,但是其防止是有限的。因此,在使用时尽量采用抑制闩锁效应的措施。在装配、运输、保管注意静电击穿IC,另外,其输入端接入电阻对防静电有防止作用。24LC16B、24LC21引脚功能见下表所示。

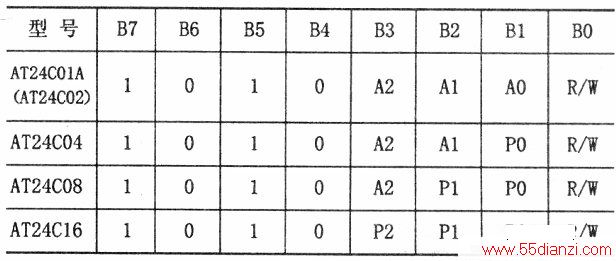

许多存储器的引脚与上表差不多,特别是24XXX系列。另外,存储器在IIC总线系统中是从器件,而微处理器是主器件,从器件通过从地址挂在总线上与主器件通信。而AT24CXXX的从地址是固定的。即为1010XXXX,同时可以通过下表来发现此规律。

注:

B7~B4:固定的4位;

B3~Bl:型号不同有差异;

A2、Al、AO:表示器件编号,其位数决定同一根总线能够挂接几个相同的器件;

P2、Pl、PO:器件内部块的选择;

BO:读写位元控制;

R/W:高电平为读,低电平为写。

常见存储器的识别标志见下表所示。

代换存储器时需要注意空白存储器的初始化问题。因此,存储器的代换尽量采用原型号同一应用机型的“拆机件”,这样可以“即换即用”,无需初始化。

存储器的复制方法之一:焊空存储器的两IIC总线引脚开机,等显示器无光栅断电后,再将总线焊好。

开机,微处理器会自动把数据存在存储器中,不过显示的画面可能需要调整。但是,部分微处理器不能够这样实现存储器的数据复制。存储器数据复制,一般通过读写器把正常的原始数据复制备份,或者通过网上查询获得。

存储器数据一般不同于电视机存储器可以用表的形式体现其初始数值,它是以二进制编码形式的文件。

存储器数据潦乱的原因有:显示器电路接地不良。

静电干扰、电磁干扰、开关机冲击等。

存储器损坏故障现象:场不同步、光栅偏色、有显示,但图像淡、“黑屏”、光栅带回扫线并且太亮、对比度失控、图像暗淡、开机光栅微弱、开机后数秒后自动保护、出现“超频”提示、无显示无电源指示、有光栅有画面,但是画面抖动。

计算机主机的存储器的构成原理实质上是用多个存储器芯片构成存储器系统,并使之与CPU总线正确接口。为达到简化存储器地址解码电路的目的,首先应尽量选择存储容量相同的芯片进行组合,然后将芯片地址线与地位地址总线相连,并且将剩下的高位地址线通过解码产生片选控制信号。根据对高位地址总线的解码方案不同,片选控制方法通常有“局部解码法”、“全解码法”以及“线选法”三种。计算机主机按内存的外观可以分类为双列直插内存芯片与内存条。主机的存储器与显示器中使用的存储器容量相差很大,而且型号往往不同。

在安装滤波电容时,尽量靠近存储器,而且尽量靠近存储器的电源引脚,并且滤波电容采用O.1μF陶瓷电容较多。

本文关键字:存储器 元器件特点及应用,元器件介绍 - 元器件特点及应用

上一篇:高速光电耦合器工作原理及应用